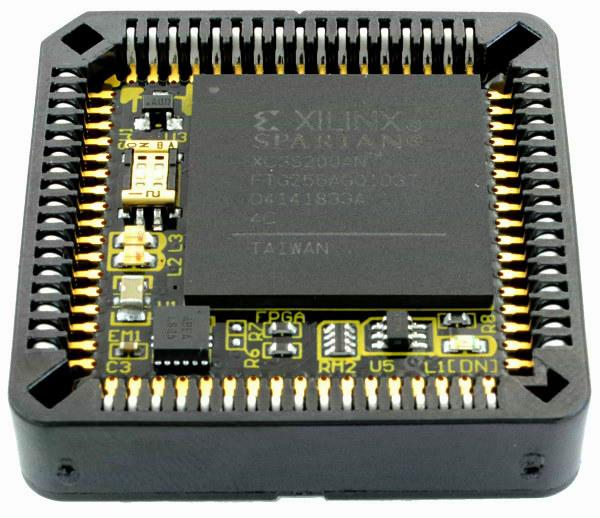

Люди приловчились так делать:

Люди приловчились так делать:

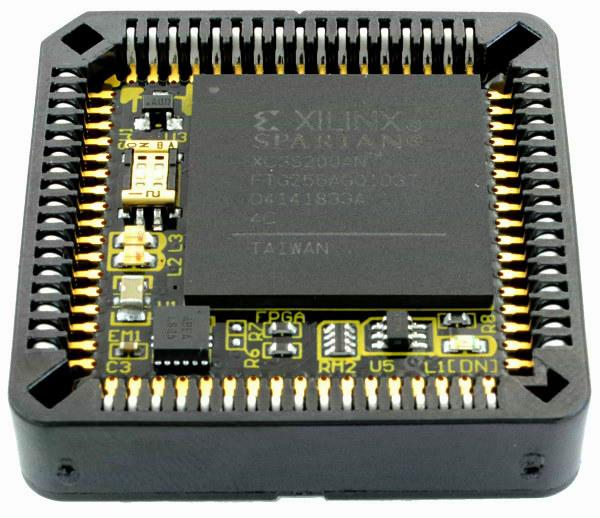

Прикольно. Только чего они этой конструкцией добивались?

Решено, ставлю Циклон3. Я конечно Z80 поставил бы, а вот с ВМ80 с его тремя напряжениями не хочу мучатся. На u10 у меня прекрасно работает переключаемая конфигурация Специалист/Специалист_МХ. Её и хочу повторить, но с вынесенной ПЗУ. Разъёмы ISA или какие-нибудь ещё не хочу ставить. Я уже задавал вопрос для чего? Ответ - для будущих разработок меня не устраивает.

Есть такие.

Нужно подумать. У самого 5 штук заволялось. Преобразовать с 5 на 3,3В можно простым резистором на 300 Ом, обратно не нужно - уровень должен ТТЛ схемой подхватиться.

Ну это конечно перебор. Ewgeny7 в u10 ставил скорость в 4 раза больше - невозможно в игры играть, решили оставить х1 и х2. Нужно что-то одно поставить либо DIP40 либо эмуляция в FPGA.

Пока сочиняю схему. Смотрел на днях даташит Циклона 3. Он имеет в своём распоряжении 423936 битов памяти, что составляет 51,75 кБайт. Можно всё ОЗУ отдать под основное + ОЗУ цвета. Внешними микросхемами памяти будут: RAM-диск на 512 кБайт и ROM-диск с "Стандарт" ПЗУ объёмом 64 кБайта. Если хватит пинов Циклона 3, то вотку ещё внутрь контроллер дисковода.

Тогда не хватит. Добавим SRAM 64 кБайт на 16 бит данных, например CY7C1021.

С любовью к вам, Yandex.Direct

Размещение рекламы на форуме способствует его дальнейшему развитию

Как не крути, а на выводы от/для процессоров пинов от EP3C5E144C8N (Cyclon 3) не хватает. Всего пользовательских пинов 82:

1. От процессоров (данные и адреса) - 8+16=24

2. От ОЗУ 512 кБайт и ПЗУ 64 кБайт - 8 + 19=27

3. От ОЗУ 64 кБайт - 16+16=32

Итого - 24+27+32=83

А ещё нужны пины под управление памятью, процессоров, VGA монитор, данные для контроллера дисковода и ПВВ "программатора".

Так что процессоры будут не "железными", а встроенными.

Вот блок-схема проекта. Таймер я ещё не выбрал.

Последний раз редактировалось fifan; 14.12.2013 в 10:17.

А зачем тебе две срамины? Поставь одну 16 бит 512Кб. К тому-же, младшие биты адреса можно для ОЗУ и ПЗУ одинаковые сделать.

Шина адреса и данных - должны быть общими для всех чипов кроме процессора. Выборка как и обычно сигналами выборки кристалла и еще пара сигналов для не 8-ми битной памяти. А если использовать прозрачный доступ к памяти - можно все вообще на одну шину вешать и выборку видео и прочего - делать во всремя не активного клока процессора. Тем более что память скоростная - можно выбирать сразу строку из внешней памяти и переносить во внутри циклоновский рам в буфер строки.

Amiga 1200+Blizzard 1260 72 Mb+Mtek 68030,Compozit 128, Leningrad 2,

Atari STE 1040,ZX Spectrum +2,Pentagon 48, Speccy2007 - 2 , ATAS 256k.

ZX Evo 4Mb- в строю.

Speccy2010 v1

Специалист (пока готовлюсь к восстановлению).

Это все мое!

Родное!

Все люблю на свете я! Это родина моя!

В u10 в конфигурации Специалиста используются две старины по 512 кбайт, 8 бит. Одна на рамдиск, другая - основное ОЗУ и видео ОЗУ. Так же использовать две по 512 или одну на 1МБайт расточительности - не все будет задействовано. Общие шины адреса и данных - в принципе можно. Но для процессоров нужно согласовывать уровни шины данных. Если использовать два процессора и объединить шины адресов и данных, то за отсутствием сигналов выборки кристаллов, необходимо управлять подачей питания. Для включения питания на процессоры хочу использовать полевик BS250, как в тестере микросхем.

По крайней мере адрес для основного ОЗУ не формируется процессором, вернее не всегда, он складывается из адреса синхрогенератора. Брать напрямую адрес с процессора для всех устройств не получится.

Ещё столкнулся с проблемой формирования импульсов синхронизации Ф1 и Ф2. Опять применять К155ЛА8? Хватит уровня в 3,3 В для входов данной микросхемы?

Вот предварительная схема. У основной ПЛИС не хватает ног для контроллера дисковода - поместил во вторую.

Последний раз редактировалось fifan; 14.12.2013 в 21:46.

Эту тему просматривают: 1 (пользователей: 0 , гостей: 1)