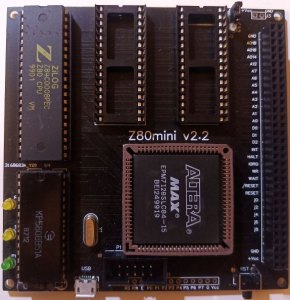

Решил я, пока еще корона не доконала, осуществить свою мечту - сделать платку мини компа на Z80 и EPM7128 - очередной велосипед, короче. На плате расположены: CPU, ROM, RAM, CPLD, UART. Предполагается возможность дальнейшего расширения методом бутерброда через системный разъем. Часть выводов CPLD остались свободными, поэтому МГТФ в ограниченном объеме тоже допускается. Основные желания, томившие мой мозг - помучить EPM7128, спроектировать и заказать 4-х слойную плату, поупражняться в написании чего-то на ассемблере Z80.

Прошу высказывать критические замечания, предложения, советы. На данный момент прототипы уже у меня в шаловливых руках. Если есть единомышленники, готовые помочь в написании и отладке кода, вышлю таковым экземпляр платы, при условии оплаты пересылки.

z80mini.zip

Добавил в архив проект для Quartus II 13.0sp1

Обновил проект. Для совместимости с Аюшей изменил порты: управление памятью (38h, бит 0, 0-ПЗУ, 1-ОЗУ), консоль (08h, 09h). Конфигурация памяти пока такая: нижняя страница памяти 32к переключается ПЗУ/ОЗУ. При сбросе выбирается ПЗУ.

Для реализации прерываний от последовательного порта нужно поставить перемычку между выводом 14 U4 (RXRDY) и выводом 54 U3 - назовем эту цепь IRQ - запрос прерывания при приеме очередного символа последовательным портом.

Пожалуй, необходимости во втором кварце на 7.3728 МГц нет. Все нужные частоты вполне может выдавать ПЛИС делением 20 МГц. Возможно, имеет смысл попробовать поставить кварц на 32768 Гц?

Ошибки на плате:

Скрытый текст

1 - вывод 25 U1 Z80 /BUSRQ висит в воздухе, для корректной работы процессора надо подтянуть его к питанию через резистор 10к.

2 - конденсатор C5 ошибочно подключен к земле, должен быть подключен к + питания. Можно повесить его с обратной стороны платы между 2 и 16 выводами U2. Такой же конденсатор желательно подключить между 15 и 16 выводами U2.

3 - "лишний" сигнал A18 на системном разъеме.

4 - второй кварц на 7.3728 МГц оказался ненужным, можно его вообще не устанавливать или использовать какой-то другой, например 32768 Гц.[свернуть]

UPD. Обновил прошивку CPLD. Адаптировал и проверил работу монитора Freddy. Для его запуска достаточно только изменить значения CONSD на 08h, CONSC на 09h, BANK на 38h.

asm8080.rar - ассемблер.

Вышла вторая версия платы - Z80mini V2.0

Основные отличия:

- плата двухслойная

- COM порт заменен на microUSB (мост TTL-USB CH340G)

- питание платы так же полностью от USB

- изменен системный разъем - перенесен на край платы и переработан - теперь будет возможность без резки дорожек делить память на сегменты по 16к и совмещать их в произвольном порядке.

- кварц заменен на генератор - можно использовать до 50МГц (больше не пробовал).

Все имеющиеся CMOS версии Z80 уверенно запустились на этой плате на 20МГц. Все имеющиеся КР580ВВ51А стабильно заработали на 115200. Импортные 82C51 можно гнать и быстрее.

Ошибки на плате V2.0: перепутаны сигналы RX TX и RTS CTS между ВВ51 и CH340G, неправильно разведена кнопка сброса.

z80mini_2.rar

Схема без ошибок.

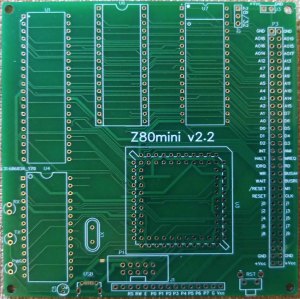

Норая версия платы- v2.2 Исправлены ошибки, внесены небольшие изменения.

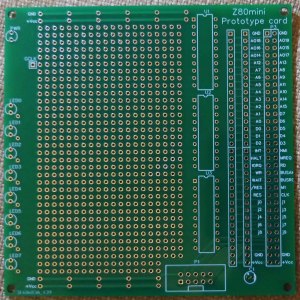

Макетная плата для проекта. Предусмотрена установка буферных элементов либо регистров, кварцевого генератора, светодиодов.

Архив проекта Quartus 13.0sp1 и готовая прошивка ПЛИС z80mini_2.rar

Генератор 50МГц, процессор 20МГц и UART 57600. Порты: управление памятью (38h, бит 0, 0-ПЗУ, 1-ОЗУ), консоль (08h, 09h).

Гербер последней версии платы - Gerber_PCB_z80mini2_4.zip

Прошивки от камрада dmtr: поддержка CF, поддержка встроенных GPIO, конфигурируемый GPIO и SPI.

Купить плату можно здесь.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию