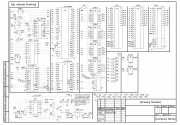

Немного захандрил, совсем было лень делом заниматься, поэтому начал рисовать схему ЮТ.

Итак, базовое направление по схеме и идеологии:

Сразу скажу, что бы не было вопросов - полное до компонентов соответствие оригиналу меня заботит мало, должна быть полная программная совместимость, что бы по возможности, те 3-4 программы для минимального модуля работали. Поэтому будет по возможности использована современная элементная база, в т.ч. и SMD для снижения потребления и размеров платы.

Делаю с дальним расчетом загнать все что можно в программруемую логику потом... Пока есть желание запустить и поиграться с тем же сопроцессором.

Почему плата содержит монитор-F: Потому, что через UART планируется подключить её к терминалу, и работать в том же мониторе-F, который будет поддерживать как вывод на видеоадаптер, так и к примеру на COM порт.

Желаемые цели: (не факт, что всё удастся сделать, но почему бы не поставить программу максимум)

1. Максимальная совместимость с оригиналом в плане процессорного модуля для начала.

2. Встроенный преобразователь напряжения +5В в +12 и -5 на плате.

3. Встроенный математический сопроцессор, подключенный на порт (А2-А3).

4. Полная дешифрация адресов I/O по встроенной в плату периферии (пока сделано на ПЗУ, потом сделаю на GAL или MAX7000)

5. Сквозная прозрачная запись в ОЗУ по адресам ПЗУ, т.е. можно будет из мониторов скопировать их содержимое в ОЗУ по адресам посадки мониторов, отключить ПЗУ и работать уже с мониторами из ОЗУ.

6. ПЗУ отключаемы через регистр на стандартном порту Е0.

7. ОЗУ 64К, оба монитора 0 и F будут размещены в общем ПЗУ.

8. 580ВИ53 по адресам 50-53. Входы выходы используются для музыки, генерации тактового сигнала для ВВ51, и для чего угодно.

9. 580ВВ55 по адресам F8-FB. Сигналы будут выведены на разъем PLS.

10. 580ВВ55 по адресам F0-F3. Сигналы будут выведены на разъем PLS.

11. AY3-8910 по адресам 70-71. Оба порта так же будут выведены на разъём.

11a.Технически к этим портам можно подключать ROM-Disk и т.п, индикаторы, платы реле, принтер и всё что угодно.

11.б. Системная шина так же будет выведена на разъём.

12. 512ВИ1 или аналог. по адресу А4-А5.

13. 580ВВ51 или 16С550 по адресам D0-D7 - вывод на терминал.

14. Вторая 580ВВ51 или 16С550 по адресам D8-DF - для чего угодно.

15. Индикаторы работают по адресам ОЗУ (9000-9002) до первого обращения процессора в область I/O 90-92. После чего, запись в индикаторы по адресам ОЗУ будет прекращена для того, что бы при работе программ их можно было задействовать.

16. Убрал 176ИЕ5. Секундные импульсы будут сниматься с 512ВИ1.

17. Запуск на этой плате ч/з терминал той же СР/М

Для начала - схема включения процессора, памяти и сопроцессора. Остальное позже. Не готово ещё.

Предложения принимаются

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию