..

Не очень сложно написать эмулятор 32-разрядного процессора, полностью совместимого с архитектурой PDP-11, но сначала полезно понять, какой должна быть его архитектура.

Первое, что приходит в голову - 22-разрядная и 32-разрядная архитектуры памяти не должны пересекаться по масштабу, поэтому минимальный блок распределяемого 32-разрядного адресного пространства должен иметь размер 222 ( 4 Mb ), а значит - режимы доступа и другие атрибуты распределяемой памяти должны задаваться для регионов, состоящих из целого числа таких блоков. 16-разрядные регионы возможны двух типов - совмещённых программ и данных ( размером 1 блок ) и разделённых программ и данных ( размером 2 блока ). Размер создаваемого 16-разрядного региона автоматически задаёт его тип. 32-разрядные регионы могут быть только совмещённого типа, поэтому непосредственные данные 32-разрядного кода всегда находятся вперемешку с кодами команд.

Количество 16-разрядных регионов не ограничено, поэтому страница ввода/вывода каждого такого региона эмулируется процессором ( с возможностью мапить отдельные адреса ввода-вывода на совместимые устройства реальной 32-разрядной шины ).

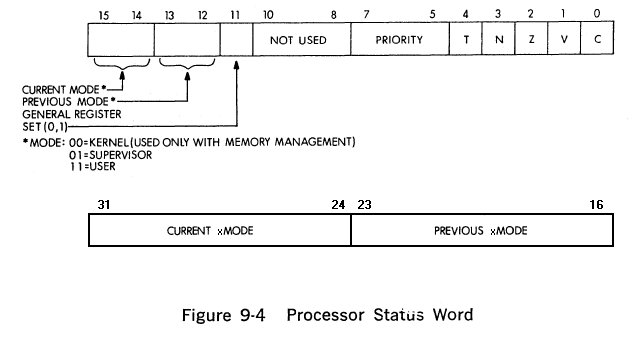

Каждому 32-разрядному процессу выделяются все 232 байтов виртуальной памяти. Номер выполняемого процесса задаётся в PSW и называется "мода":

Нулевой процесс имеет особые привилегии и выполняется в адресном пространстве KERNEL-моды. Максимальное число процессов составляет: 256*3 = 768 ( из-за недопустимости номера моды 2 - все 256 номеров, оканчивающихся на 2, выпадают ).

Процессор сохраняет/восстанавливает контекст при смене региона исполнения кода, поэтому только от операционной системы зависит, выполнять каждую программу в отдельной моде, выполнять все программы в различных регионах общей моды или использовать смешанную стратегию.

...

Первый 4Мб блок адресного пространства KERNEL-моды содержит вектора прерываний и начальный KERNEL-стек, последний 4Мб блок KERNEL-моды содержит блок ввода-вывода со стартовым ПЗУ и регистрами внешних устройств.

Относительно организации ввода-вывода в 32-разрядном режиме полной ясности нет. Возможно, оптимальным является вариант, когда при включении питания создаётся единственный одноблочный 4Мб регион ввода-вывода в конце адресного пространства, но впоследствии операционная система может создавать дополнительные регионы ввода-вывода произвольного размера ( кратного 4Мб ). Чтобы разделить на шине доступ к памяти и доступ к устройствам - шина должна иметь дополнительную линию ( фактически расширяющую непосредственно адресуемое пространство до 233 ).

...

При выполнении команд процессор предъявляет только одно требование к выравниванию кода - команды должны начинаться с чётных адресов. 16-разрядные команды могут содержать от 1 до 3 = 16-разрядных слов с одним словом кода команды, 32-разрядные - от 1 до 6 ( или более? ) 16-разрядных слов с одним или двумя словами кода команды.

Размер поля 32-разрядной команды увеличивается ( по сравнению с 16-разрядной командой ) с 3 до 4 битов, поэтому помимо регистров R0..R7 появляются ещё 8 регистров, назначение которых предстоит определить. Также появляются 7 дополнительных способов адресации ( каких? ). 8-й набор битов адресации ( например ^b1111 ) резервируется. В позиции источника ( т.е. для битов 15,14,13,12 ) такой набор является признаком отсутствия у кода команды второго слова. В результате - однословные команды имеют 15 вариантов с использованием младшего байта ( в качестве кода приёмника или байтовой константы ) и дополнительно - 256 вариантов однобайтовых команд.

Двухсловные команды могут задавать размер отдельно источника и приёмника в 1, 2 или 4 байта - для чего выделяются младшие 4 бита второго слова команды ( по два бита на размер источника и размер приёмника ). Поле позволяет задавать также размер источника и/или приёмника в 8 байтов, но в текущей реализации это недопустимо. Остаток даёт 4095 различных команд с источником и приёмником и дополнительно ( для кодов команд с единицей в старшем разряде второго слова ) - более 4000000 команд, не удовлетворяющих стандарту PDP-11 на кодирование источника и приёмника.

...

Относительно специального назначения дополнительных регистров процессора. Видится необходимым наличие регистра базы региона кода ( задающего постоянное смещение для PC ), регистра базы региона стека ( задающего постоянное смещение для SP ) и регистра базы региона данных ( задающего постоянное смещение для косвенной адресации обычных регистров ). База кода может изменяться только в KERNEL-моде, потому что её изменение приводит к переключению исполняемого потока, относительно порядка изменения базы стека ясности нет, а регистр базы региона данных - скорее всего может изменяться пользователем для доступа к собственному региону кода или стека, как к данным.

Если дополнительные способы адресации будут предусматривать использование индексных регистров - ещё два регистра надо отдать для индексного регистра источника и индексного регистра приёмника. Остаются три регистра - R8, R9, R10 ( или RA ? ), которые можно использовать как дополнительные регистры общего назначения. Если конкретная программа не использует индексную адресацию - индексные регистры также могут использоваться ею в качестве регистров общего назначения. При косвенной адресации относительно индексного регистра - регистр базы данных используется так же, как и при косвенной адресации относительно обычных регистров.

Регистры базы могут непосредственно использоваться в команде только с режимом адресации 00.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию