шото я туплю - не совсем ясно-прозрачно, почему доступны 2Кх4, а не 8Кх4

шото я туплю - не совсем ясно-прозрачно, почему доступны 2Кх4, а не 8Кх4

Последний раз редактировалось Клапауций68; 17.01.2019 в 08:52.

С любовью к вам, Yandex.Direct

Размещение рекламы на форуме способствует его дальнейшему развитию

разобрался - адресная шина 11-бит

походу - финал-финал.

v1.0 - актуальная.

https://github.com/Klapautsiy/The-di...MK-85/releases

Последний раз редактировалось Клапауций68; 20.01.2019 в 10:07.

Здравствуй Клапауций,

Цитата из личного сообщения:

Я думаю, что проблема возникает из-за неполного декодирования адреса. Как видно на приведённом раньше рисунке, отдельные микросхемы ОЗУ 2кБ должны выбираться логическим сложением одного из сигналов !CE2-!CE5 с одном из сигналов !CE7-!CE8. Если общий размер ОЗУ не превышает 6кБ, можно применить упрощённую схему и обойтись только сигналами !CE2-!CE4. Но в случае 8кБ, без применения сигнала !CE8 память будет видна дважды в диапазоне адресов 0x8000-0xBFFF (первая копия в диапазоне адресов 0x8000-0x9FFF и вторая в диапазоне адресов 0xA000-0xBFFF).всё работает ровно так, как описано, но никак для меня непрозрачно/понятно - почему всё-таки счётчик показывает 15557, а не 7365 ?

что ему не так?

если есть свободное время - ответь, пожалуйста, в этой теме

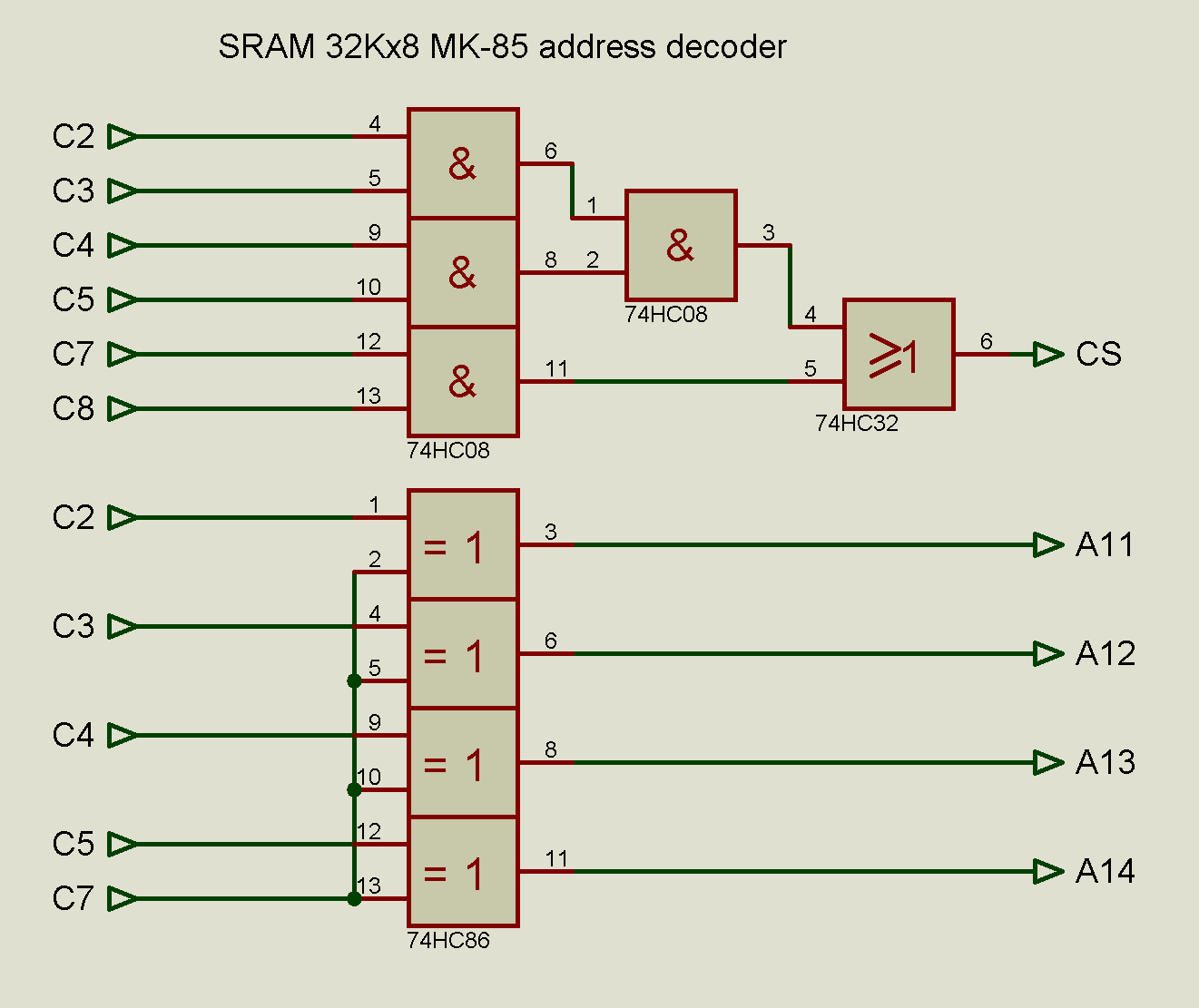

Сигнал !CS для микросхемы CAT71C256L-85 должен формироваться по формуле:

(!CE2 and !CE3 and !CE4 and !CE5) or !CE8

Последний раз редактировалось piotr433; 20.01.2019 в 13:20.

вот оно чё, Михалыч - осторожно следует... чрезвычайно осторожно.Особо нужно подчеркнуть, что наращивать радиолюбительский компьютер следует чрезвычайно осторожно...

И. КРЫЛОВА

- - - Добавлено - - -

т.к. я прекратил тупить, считая, что в МК-85 используется 1-й вариант распределения памяти(см. рисунок), то становится понятно, что доступная память не 8Кх4=32К, а 2Кх8=16К.(3-я конфигурация)

и эту память можно вычитать, дешифруя логические состояния пинов процессора С2-С5/А12-А13 в уникальные комбинации пинов SRAM CS/А11-А14.

альфа версия схемы - возможно получится оптимизировать/упростить:

таки, коллега.

- - - Добавлено - - -

здесь можно потыкать палкой дешифратор SRAM.

проект Proteus 8 в приложенном файле:

Я бы ещё хотел обратить внимание на один нюанс. Применение сигналов CE микропроцессора в качестве адреса кажется мне не совсем безопасным - может не удовлетворять требованиям ОЗУ на временные параметры tAS (время задержки сигнала "запись" относительно сигнала адреса) и tWR (время сохранения сигнала адреса по окончании сигнала "запись"). Под термином "запись" подразумевается одновременный низкий уровень сигналов CS и WE.

Микросхема CAT71C256L требует tAS > 0 наносекунд и tWR > 5 наносекунд.

временные диаграммы сигналов микропроцессора при записи

временные диаграммы сигналов ОЗУ при записи

да, Piotr - я читал заметки об этом нюансе.

и пришёл к выводу, что самым оптимальным способом понять, вписываются ли таймауты работы устройства в режим стабильной работы - просто провести программный стресс-тест.

возможно, существуют другие дешёвые способы проверить стабильность работы SRAM в такой аппаратной конфигурации, но я их не знаю.

Эту тему просматривают: 1 (пользователей: 0 , гостей: 1)