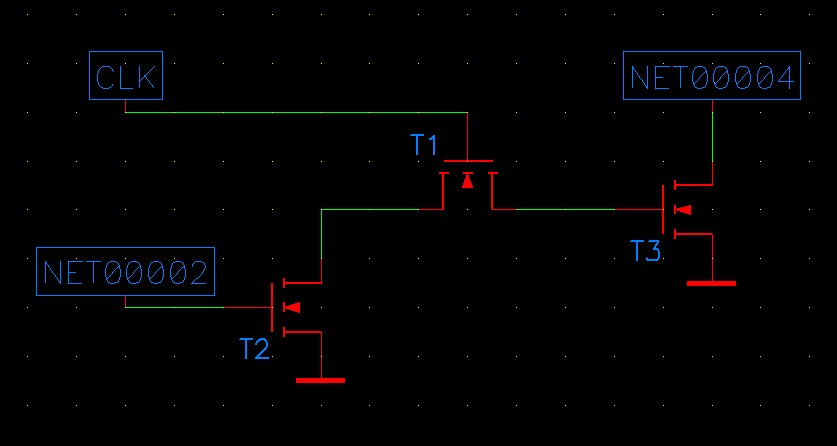

Это я в курсе) Я же твой ВМ2 весь переводил из транзисторной схемы в логическую)

- - - Добавлено - - -

Возьмем для примера, что я нарисовал за сегодня 50 транзисторов.

А всего их допустим 6800. Делим 6800 / 50, получается всего 136 дней)

А сколько ты ВМ2 рисовал? И сколько ВМ80?

Ответить с цитированием

Ответить с цитированием