Сообщение от

Denn

"Контроллер" на ВВ55 без каких-либо проблем работает с двумя устройствами на 40-проводном шлейфе стандартной длины, никаких тепличных условий не требуется. На черепашьей скорости дрыганья сигналами никакие "спецэффекты" шлейфов не проявляются.

Ты так пишешь, как будто контроллер семейства НЕМО-IDE (будь то на Спеке, Орионе-ПРО или АТМ или еще где) работает в 1000500 раз быстрее. Там разница по скорости всего лишь в 2 раза (причем в самой поедающей процессорное время процедуре - чтения/записи 512б. сектора - эта разница так и вообще всего 1.7 т.е. менее чем в 2 раза). Схема на 8255 лучше работает (как мне кажется) потому, что там все управляющие сигналы IDE длинные т.к. формируются программно процессором - на каждый полумеандр сигналов шины управления IDE выходит по несколько тактов процессора между двумя соседними записями в 8255, т.е. баланс по времени (разнесение фронтов по времени что дает стабильность) между записью в регистры 8255 (которые 16-битная шина) и длительностью управляющих сигналов, переносящих состояние этой шины в регистры IDE.

А в схемах NEMO-like запись второй (первая кладется в выходной регистр контроллера без уведомления IDE) половинки 16-битного слова шины сопровождается "иголкой" сигнала управления на шине управления IDE чтобы записать это 16-битное число. Вот тут что-то за чем-то и не успевает на некоторых приводах.

Вот для примера растактовка этой самой п.п. записи блока и для контроллера и для "контроллера" (второй из которых при том полностью сохраняет исходную функцию ППА - хоть программатор или принтер вместо HDD подключай). На которой кстати видно, что сигналы управления не падают по фронту приходящих данных (как это делают схемы НЕМО-IDE)

Код:

write_data:

; call MDI

IF IDEPRO

ld b,0

WRC0: ld c,(hl) ; 7

inc hl ; 6

ld a,(hl) ; 7

out (PRO_DATAH),a ; 11

inc hl ; 6

ld a,c ; 4

out (PRO_DATAL),a ; 11 total 52 tstates

djnz WRC0

ELSE

ld a, wr_ide_8255

@@P0: ld (ide_8255_cfg), a

ld bc, ide_data

@@P1: ld de, ide_8255_ctl

wrblk2: ld a, (hl) ; 7

@@P2: ld (ide_8255_lsb), a ; 13

inc hl ; 6

ld a, (hl) ; 7

@@P3: ld (ide_8255_msb), a ; 13

ld a, c ; 4

ld (de), a ; 7

or ide_wr_line ; 7

ld (de), a ; 7

inc hl ; 6

ld a, c ; 4

ld (de), a ; 7 total 88 tstates

djnz wrblk2

ld a, rd_ide_8255

@@P4: ld (ide_8255_cfg), a ; config 8255 chip, read mode

ENDIF

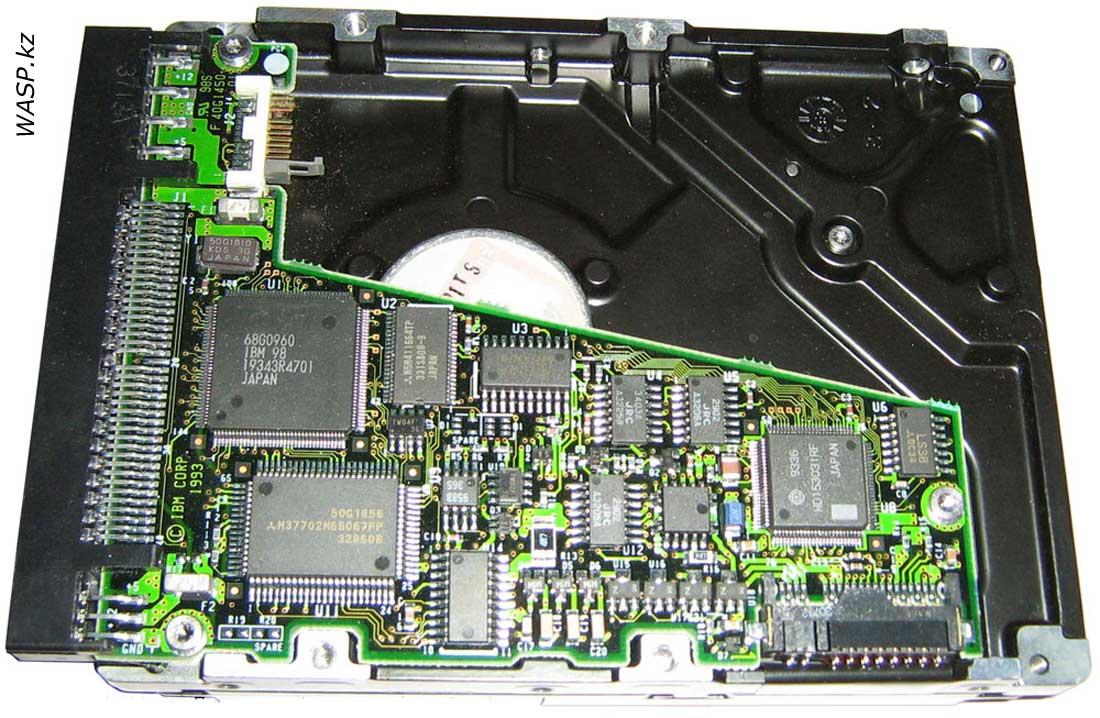

Были у меня на что-то около 200Мб, но те были 2.5" от нутбуков, т.е. все равно существенно посовременнее чем маломерные 3.5".

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию