PROFI IF is actually in development and contain reprogrammable CPLD. All features and ports can be modified during development.

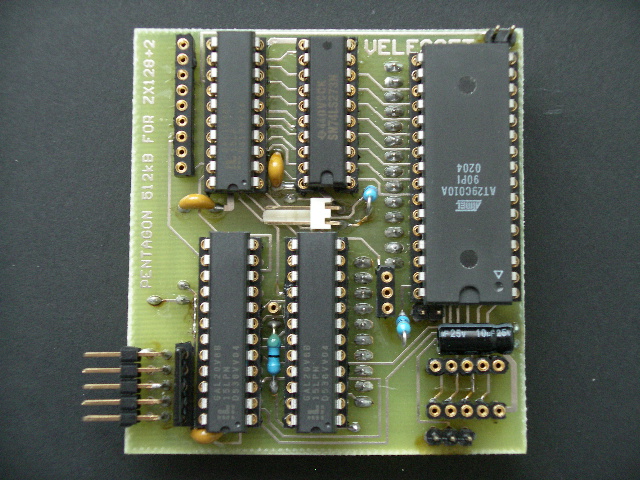

My first upgrade is PENTAGON INTERFACE:

http://velesoft.speccy.cz/pentagon512_interface.htm

PROFI INTERFACE will compatible, but more powerfull

New NMI button will jump to extra NMI menu without rewriting memory on stack pointer (it's planned feature). I/O adress space can be mirrored to extra memory and user can read from memory last writed values to ports

Possibility block extra memory for users (128kB only) and enable extra memory (1MB) only for trdos rom (ramdisc will protected).

Advanced memory paging in low 16kB (as rom replacement) = DivIDE emulation

INFO ABOUT DIVIDE INTERFACE:

http://velesoft.speccy.cz/zx/divide/index.htm

Yes, it can be implemented to PROFI INTERFACEI propose to use the following specification of ports:

Код:#BDDD/48637 1011110111111101 10xxxx0xxx0xxx01 rd #DFFD #BDFD/48605 1011110111111101 10xxxx0xxx1xxx01 rd #1FFD #BFDD/49117 1011111111011101 10xxxx1xxx0xxx01 rd #FE #BFFD/49149 1011111111111101 10xxxx1xxx1xxx01 rd #7FFD

---------- Post added at 21:07 ---------- Previous post was at 20:59 ----------

I will support more different rom paging ports:

DIVIDE rom memory on port 227

MB02 rom memory on port 23

ZX rom memory on port 7FFD/1FFD (+2A/+3/Scorpion)

1MB Ram paging ports:

7FFD (Pentagon 1024)

7FFD+1FFD (Scorpion)

7FFD+DFFD (ZX PROFI)

MB02 PAGING PORT 23:

port layout:

D0-D4 - number of 16kB rom/sram page (0-31)

D5 - 1=write enable or 0=write protect low 16kB memory

D6 - 1=connect sram memory (only if D7=0)

D7 - 1=connect rom memory (only if D6=0)

If D6=0 and D7=0 then will MB02 memory disabled and ZX rom is connect in

low 16kB

If D6=1 and D7=1 then will reset Z80CPU + disabled ZX rom + connect

external MB02 rom page 0 with write protect (set memory port to value #80)

Ответить с цитированием

Ответить с цитированием