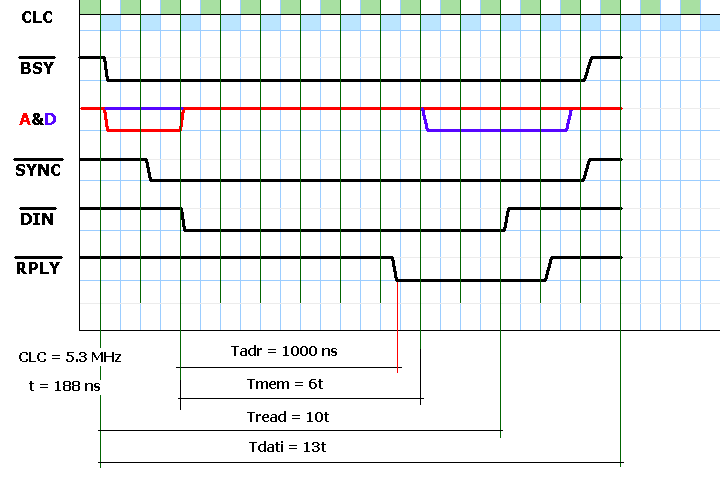

Об том и речь. Цикл чтения включает синхронные (строго тактированные) и асинхронные части. Насколько я понял из проведённых осциллографических исследований (весьма далёких от идеала) все синхронные части цикла чтения у ВМ1 занимают в сумме 6 тактов.

Т.е. на первый взгляд - можно было бы уточнить пресловутую формулу 8T + tn как ( 6T + tn ) + 2T. Но дело в том, что время между выставлением DIN/DOUT и приходом RPLY - это не единственный асинхронный участок цикла DATI, поэтому (по большому счёту) пресловутая формула 8T + tn вообще лишена смыслового содержания.

---------- Post added at 12:42 ---------- Previous post was at 12:31 ----------

Я свои наивные мысли по этому вопросу начал даже излагать в специальной теме.

Если осциллографическое исследование 1801ВМ1 продолжится - выложу там полученные графики циклов шины, типа такого:

Ответить с цитированием

Ответить с цитированием