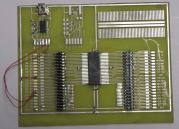

Фотоотчет о попытке подружить SRAM и FPGA.

Ver 1 чип IS61LV25616AL-10TL

Ver 2 чип CY7C1041DV33-15VI

В первом случае чип не подавал признаков жизни.

Во втором случае чип запустился, но на очень низкой частоте ~ 10 MHz.

Код модуля WB - SRAM выложу позже(надо немного причесать).

- - - Добавлено - - -

Код модуля:

Может я допускаю какую-то "детскую" ошибку или платку развел неправильно (добавить антизвонные резисторы, терминаторы)Код:module sram_wb_16 ( input wb_clk_i, input [15:0] wb_adr_i, input [15:0] wb_dat_i, output [15:0] wb_dat_o, input wb_cyc_i, input wb_we_i, input [1:0] wb_sel_i, input wb_stb_i, output wb_ack_o, //----------------------------------- output [17:0] sram_adr, output sram_nOE, output sram_nWE, output sram_nCS, output sram_nUB, output sram_nLB, inout [15:0] sram_data ); wire w_ena; wire r_ena; wire [1:0] ena; reg [12:0] ack; reg [15:0] d,r; assign sram_nCS = 1'b0; assign sram_nUB = 1'b0; assign sram_nLB = 1'b0; assign sram_adr[17:0] = {5'b00000 ,wb_adr_i[13:1]}; assign wb_dat_o = sram_data; assign w_ena = (wb_we_i & wb_cyc_i & wb_stb_i); assign r_ena = (~wb_we_i & wb_cyc_i & wb_stb_i); assign sram_nOE = ~r_ena; assign sram_data =(w_ena)? wb_dat_i: 16'hzzzz; assign sram_nWE = ~w_ena; assign ena = wb_we_i ? wb_sel_i : 2'b11; assign wb_ack_o = wb_cyc_i & wb_stb_i & (ack[10] );//| wb_we_i); always @ (posedge wb_clk_i) begin ack[0] <= wb_cyc_i & wb_stb_i; ack[1] <= wb_cyc_i & ack[0]; ack[2] <= wb_cyc_i & ack[1]; ack[3] <= wb_cyc_i & ack[2]; ack[4] <= wb_cyc_i & ack[3]; ack[5] <= wb_cyc_i & ack[4]; ack[6] <= wb_cyc_i & ack[5]; ack[7] <= wb_cyc_i & ack[6]; ack[8] <= wb_cyc_i & ack[7]; ack[9] <= wb_cyc_i & ack[8]; ack[10] <= wb_cyc_i & ack[9]; ack[11] <= wb_cyc_i & ack[10]; ack[12] <= wb_cyc_i & ack[11]; end endmodule

Ответить с цитированием

Ответить с цитированием