С любовью к вам, Yandex.Direct

Размещение рекламы на форуме способствует его дальнейшему развитию

А обычно на него и реагируют только при записи (DOUT) байта.

Хотя, конечно, мысль интересная - после приёма адреса быстрее шинные драйвера переключать, если будет НЕ ЗАПИСЬ.

Интересный тогда еще вопрос. Почему по диаграммам @Ynicky сигнал DOUT выдается через 5 тактов после SYNC (или 4 такта после окончания WTBT). Тогда как при записи DIN выдается через такт после SYNC.

- - - Добавлено - - -

В общем, внесу коррекцию в описание.

Процедура записи чтения, как есть по SYNC, а процедура записи будет по DOUT. Что байтовая, что словная.

Видимо, это сделано именно потому, что в случае записи интервал между SYNC и DOUT слишком большой, и нельзя начинать писать настолько заранее, т.к. в этот промежуток может влезть целый слот памяти. А в случае с чтением можно начинать сразу по SYNC, т.к. DIN воспоследует уже через один такт. Это на такт ускоряет процесс чтения.

- - - Добавлено - - -

Обновил 1515ХМ2-003.

- Оптимизированна схема для более легкого понимания

- Исправлены неточности

p.s.: Особое внимание требуют RS-триггеры, которые при оптимизации могут превратиться в мину замедленного действия, связанную с тем, что прямой и инверсный выход RS-триггера неравнозначны. Если на прямом выходе 0, это еще не значит, что на инверсном будет 1. И наоборот. Это связано с тем, что вход R имеет приоритет на прямом выходе, а вход S на инверсном. Или говоря проще - если на R и S установлены единицы, то и прямой выход, и инверсный будут в 0.

Поэтому при оптимизации нельзя просто так перебрасывать сигнал с инверсного выход на прямой, или же убирать один из выходов, если в схеме используются два.

В данном реверсе я допустил подобную ошибку в схеме установки RPLY, но исправил ее. И проверил все остальные RS-триггеры в схеме.

Посмотрел схему ХМ2-001, и заметил, что при чтении данных, сами данные на шину AD выставляются одновременно с сигналом RPLY. Не опасно ли для ВМ2 это делать одновременно? Или же ВМ2 не сразу защелкивает данные с шины по сигналу RPLY, а чуть с задержкой, чтобы данные успели устаканиться?

Titus(16.08.2020)

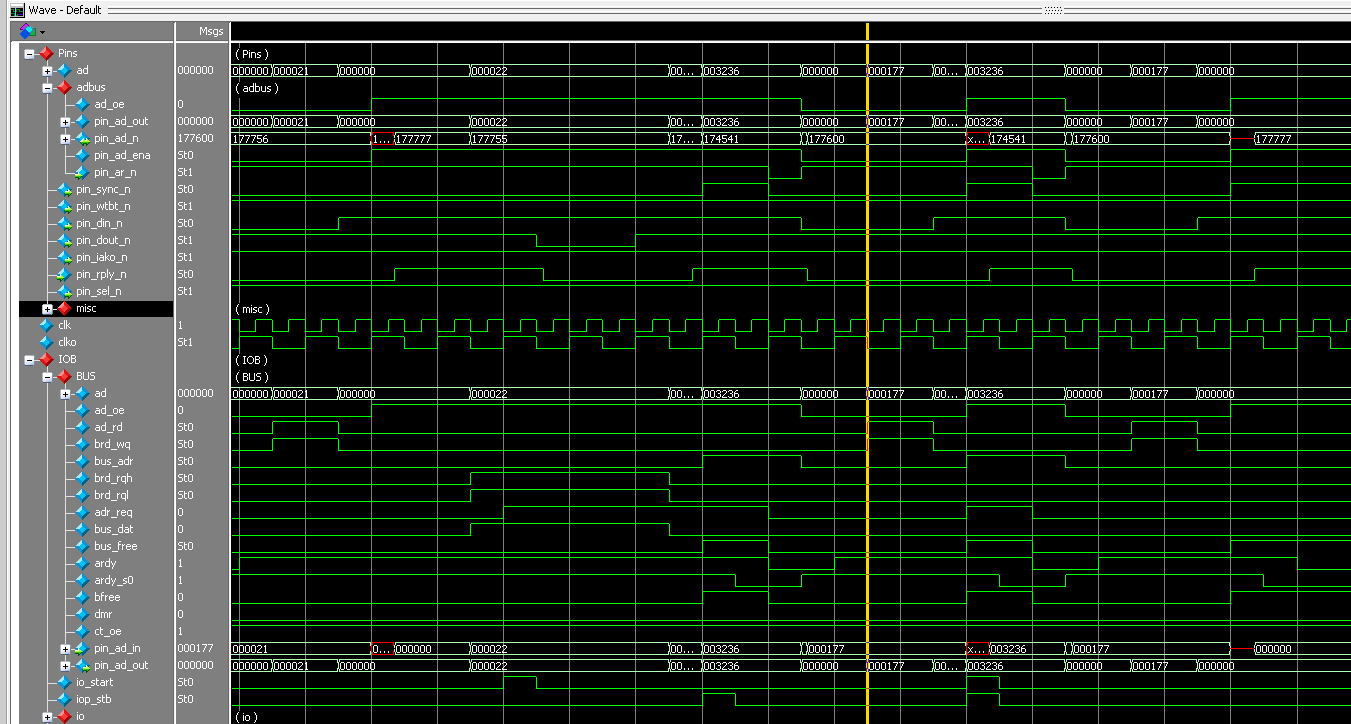

nRPLY должен поступать после активации nDIN/nDOUT, если nRPLY поступит даже мгновенно после этих стробов, то минимум проходит целый такт пока процессор защелкивает nRPLY внутри (rply0) и вырабатывает внутренний строб записи данных (bus_wq) с шины nAD во внутренний латч. Поэтому данные легко могут быть выставленны не то что одновременно с RPLY, но и до такта задержаться (а то и до двух - как повезет с соотношением RPLY с фазой F1). Стандарт МПИ, кстати, допускает выставление RPLY до данных - 200нс, как раз примерно один внутренний такт ВМ2 при внешней частоте 10МГц.

nzeemin(17.08.2020)

nzeemin(17.08.2020)

Видеовыход как будешь моделировать и получать картинку?

- - - Добавлено - - -

Я, кстати, все еще проверяю и оптимизирую реверсы, и порой нахожу неточности. Вернее, неточностей почти нет. Только изредка в RS-триггерах, т.к., как я уже писал выше, это мина замедленного действия после оптимизации, если их точно не проверить. Вот сейчас и проверяю.

Эту тему просматривают: 1 (пользователей: 0 , гостей: 1)