Одиним из случаев приостановки работы АЛУ и микропрограммы является удержание регистра адреса RA.

Регистра RA содержит адрес, выставляемый на шину AD в цикле чтения/записи. Ввиду того, что этот реигстр не буферизирован, а транслируется на шину напрямую, он требует защиты от перезаписи в то время, пока адрес удерживается на шине AD. За защиту RA от перезаписи отвечает сигнал RA_HOLD.

Работа АЛУ с регистром RA отличается от работы с другими регистрами следующими особенностями:

1. Регистр RA может обновлятся не только в конце цикла АЛУ (по WR2), сохраняя результат математическо-логической операции, но и в самом начале цикла АЛУ (по ALU_WR). Такая возможность позволяет более удобно и быстро реализовывать постинкрементные режимы адресации, когда одна операция АЛУ сперва выдает исполнительный адрес блоку ввода-вывода, а затем инкрементирует адрес, в то время, как блок ввода-вывода уже работает.

2. Каждая запись в регистр RA сразу же запрашивает цикл ввода-вывода. И если блок ввода-вывода свободен, начинается обмен.

3. Как только запрошен цикл ввода-вывода, регистр RA блокируется сигналом RA_HOLD до тех, пор, пока не будет получен ответ AR (подтверждение адреса), с задержкой до 2-х тактов (по заднему фронту сигнала RTA). Если RA заблокирован, то любой следующий цикл АЛУ/микрокоманды, обновляющий RA, будет приостановлен до тех пор, пока не будет снят сигнал RA_HOLD. Цикл, не обновляющий RA, будет работать без задержки.

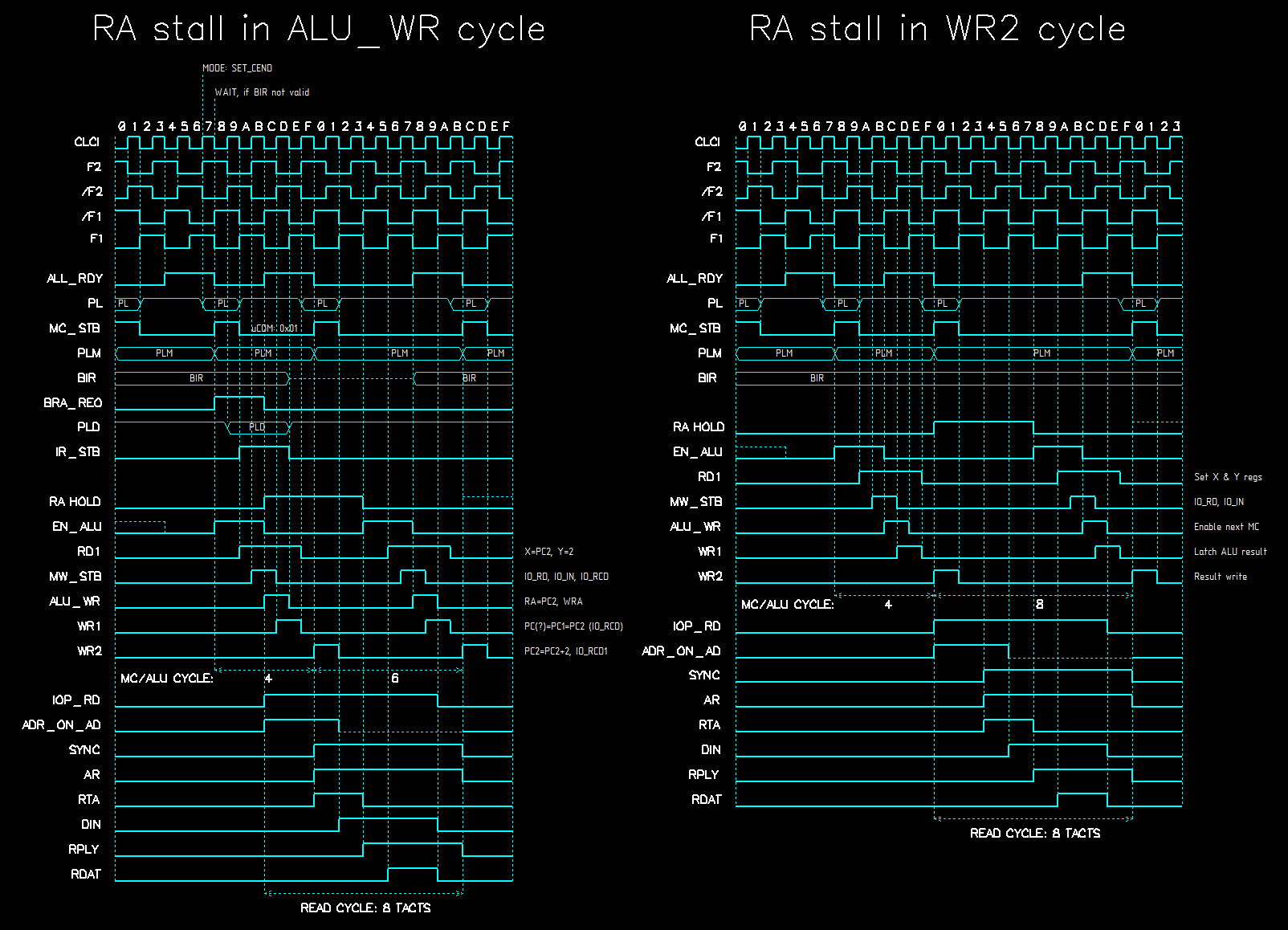

На графике приведены примеры блокировки регистра RA.

1. Слева RA обновляется в начале цикла АЛУ (по ALU_WR). Задержка следующей микрокоманды 2 такта.

2. Справа RA обновляется в конце цикла АЛУ (по WR2). Задержка следующей микрокоманды 4 такта.

p.s.: Предыдущий пост тоже обновлен и дополнен.

Ответить с цитированием

Ответить с цитированием