Модель процессора ничего не знает об УКНЦ, и о ДВК, и даже о пишмашинке "Ромашко" никогда не слышала. Поэтому никаких F1/F2 относящихся у УКНЦ тут быть не может. Логично?

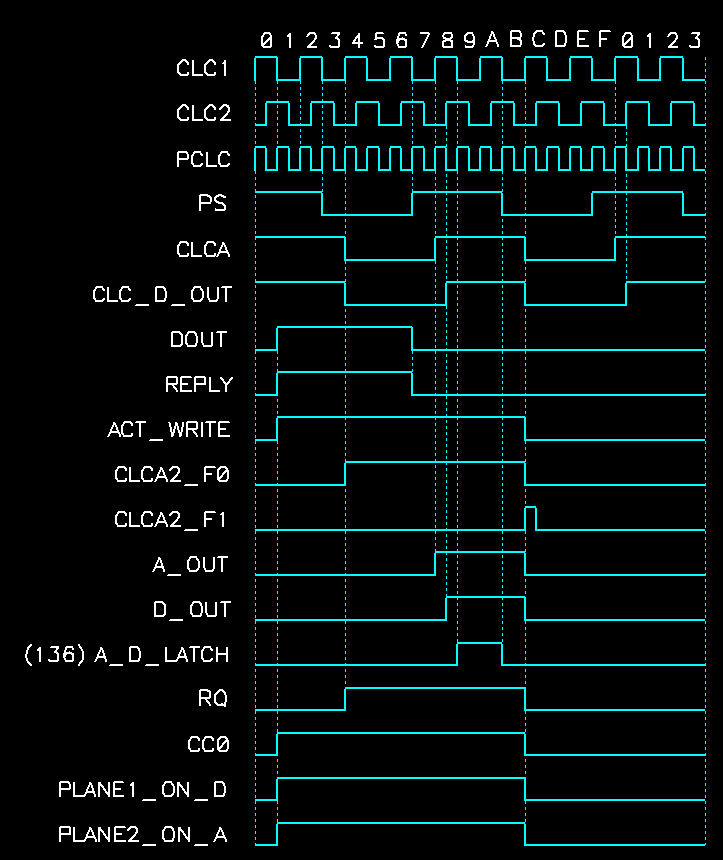

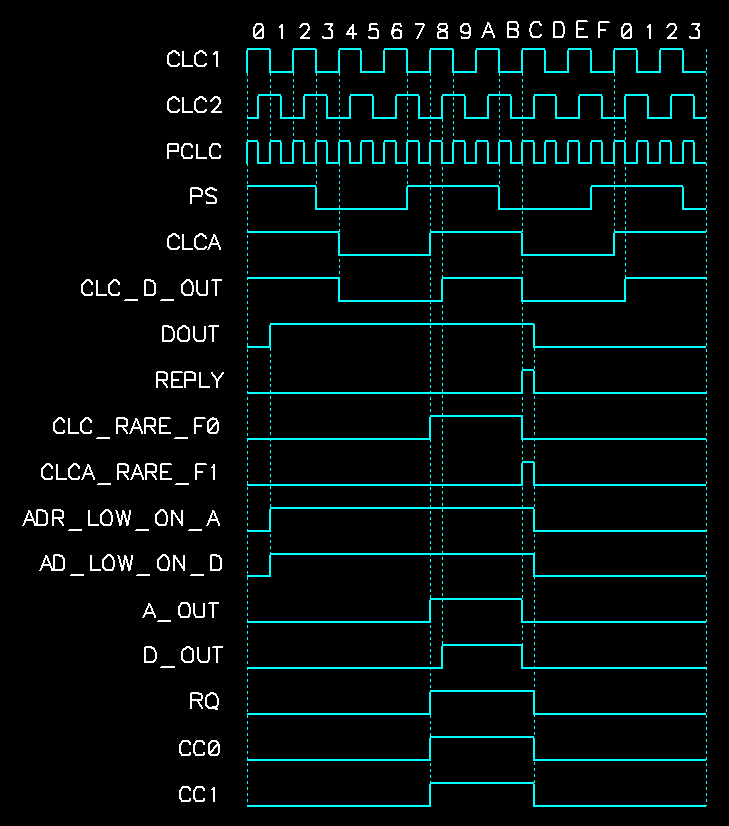

А схему процессора 1801ВМ2 ты же притащил, если ты ее откроешь то увидишь фи1, ~фи1, фи2, ~фи2. Греческих букв для именований цепей в пикад не завезли в это раз, так шо - звыняй

Ответить с цитированием

Ответить с цитированием