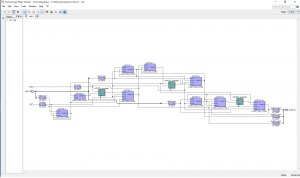

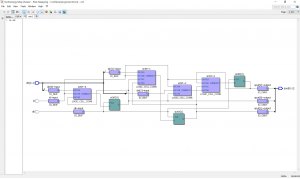

А я их сделал не по обычной схеме, а по поведенческому описанию. А уже синтезатор их переведет в схему (библиотечные элементы) как надо, в зависимости от заданных констрейнов (например рабочая частота).

mk_sCTR_LINE_ADR_L:

process (sPCLC_Q,sLOAD_LINE_ADR_L,sDGIN)

begin

if sLOAD_LINE_ADR_L = '1' then

sCTR_LINE_ADR_L <= sDGIN;

elsif (sPCLC_Q(2) = '1' and sPCLC_Q(2)'event) then

sCTR_LINE_ADR_L <= sCTR_LINE_ADR_L + "1";

end if;

end process;

Ответить с цитированием

Ответить с цитированием "Байт-48"

"Байт-48"