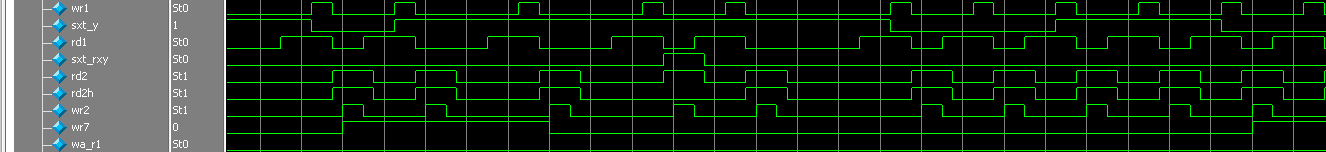

Потому что это цепь с очень высоким fan-out, здоровая шина и, соответственно, с большой электрической емкостью. Простой depletion load тут физически быстро работать не сможет - не успеет сформировать высокий уровень, поэтому поставили сдвоенный транзистор и сделали для него отдельный строб.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию