Тогда логика подсказывает только одно - выкинуть эту проверку)

- - - Добавлено - - -

Все понятно, что меня смутило)

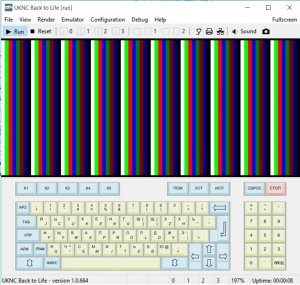

У тебя под F1 значится не F1 процессора, а F1 УКНЦ, которая в 2 раз выше.

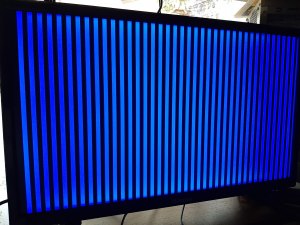

Итак, по твоему графику подтверждается, что цикл чтения с опережающим RPLY действительно занимает 6 тактов, как на моем графике.

Остается вопрос к эксперту @Alex_K, что он об этом скажет.

Ответить с цитированием

Ответить с цитированием