Titus(28.10.2020)

Ура, нашел еще одну избыточность в процессоре)

ALU производит операции над операндами, получаемых с двух внутренних шин X и Y. Операнд приемник (dd) выставляется на шину X, операнд источник (ss) на шину Y. Также на шину Y может выставляться регистр-константа или регистр-переменная для однооперандных команд.

ALU состоит из нескольких ступеней:

1. Входная ступень, здесь возможно инвертирование операндов X или Y, а также обнуление одного из операндов.

2. Вычисление промежуточных логических функций OR, AND, а также их комбинаций - XOR и CLR (обнуление результата).

3. Опциональная ступень ускоренного вычисления переносов для функции сложения.

4. Сложение по модулю два (XOR) результата ступеней 2 и 3.

5. Опциональный сдвиг результата вправо или влево с опциональным использованием флага переноса.

Кодирование операций ALU:

Все варианты операций с ALU:Код:Однооперандные операции (PL13=0): PL17 PL14 OPX OPY 0 0 0 Y 0 1 /X 0 COM 1 0 0 /Y 1 1 X 0 ROL, ROR, ASL, ASR Двухоперандные операции (PL13=1): PL17 PL14 OPX OPY ALU_G ALU_CIN 0 0 X Y 0 0 BIS, BIT, CLR, XOR, TST 0 1 /X Y 1 1 NEG 1 0 X /Y 1 1 SUB, DEC, SBC, BIC 1 1 X Y 1 0 ADD, INC, ADC ALU_G - сумматор ALU_CIN - входящий перенос для сумматора Логические функции: PL16 PL15 0 0 Функция XOR (является составной частью сложения) 0 1 Функция AND 1 0 Функция OR 1 1 Функция CLR (не используется, результат равен 0) Сдвиг результата: PL20 PL19 0 0 Нет сдвига (NSHIFT) 0 1 Сдвиг влево (LSHIFT) 1 0 Сдвиг вправо (RSHIFT) 1 1 Запрещенная комбинация PL15 - Блокирует линию OR, а также блокирует сумматор (ALU_G и ALU_CIN) PL16 - Блокирует линию AND PL18 - Разрешает флаг преноса для сдвигов Если PL17=0, PL14=0 и PL13=0, то расширение знака блокируется (SXT_Y0 = 0)

Полная маска команд, получаемая от PLM:Код:PL17 PL16 PL15 PL14 PL13 0 1 0 0 1 BIS: AF = X | Y 0 0 1 0 1 BIT: AF = X & Y 0 0 1 0 1 CLR: AF = X & Y = X & 0 = 0 (Y=0) 1 0 1 0 1 BIC: AF = X & ~Y 0 0 0 0 1 XOR: AF = (X & Y) | ~(X | Y) = X ^ Y 0 0 0 0 1 TST: AF = (X & Y) | ~(X | Y) = X ^ Y = X ^ 0 = X (Y=0) 1 0 0 1 1 ADD: AF = X + Y 1 0 0 1 1 INC: AF = X + Y = X + 1 (Y=1) 1 0 0 1 1 ADC: AF = X + Y = X + C (Y=C) 1 0 0 0 1 SUB: AF = X + ~Y + 1 = X - Y 1 0 0 0 1 DEC: AF = X + ~Y + 1 = X - Y = X - 1 (Y=1) 1 0 0 0 1 SBC: AF = X + ~Y + 1 = X - Y = X - C (Y=C) 0 0 0 1 1 NEG: AF = ~X + Y + 1 = ~X + 0 + 1 = ~X + 1 (Y=0) 0 0 0 1 0 COM: AF = ~X ^ 0 = ~X (Y=C) 1 0 0 1 0 Shift: AF = X ^ 0 = X

Немного замечаний:Код:3222222222211111111110000000000 0987654321098765432109876543210 Номер линии PL00-30 w PPIIIISSCAAAAAyyyYYxxxXW B Назначение линии __ ________ Инверсия линии .....1...........1............. XOR .....1........1..1............. BIS .....1.......1.1.1............. BIC ....11.......1...1............. SUB ....11.......1..11............. ADD .1..11..........11.........1... CMP .1...1.........1.1.........1... BIT ....11.........1.1..1.1........ CLR (Y=0) .....1.......1...1.1..1........ DEC (Y=1) (ALT_CNST=0) .....1.......1..11.1..1........ INC (Y=1) (ALT_CNST=0) ....11..........11..1.1........ NEG (Y=0) ....11.......1..11.1.11........ ADC (Y=PSW0) (Бит C) ....11.......1...1.1.11........ SBC (Y=PSW0) (Бит C) .1..11...........1..1.1....1... TST (Y=0) ....11..........1..1.11........ COM (Y=PSW0) (Бит C) ....11.....1.1..1.............. ASL (LSHIFT) ....11.....111..1.............. ROL (LSHIFT) (CARRY) ....11....1..1..1.............. ASR (RSHIFT) ....11....1.11..1.............. ROR (RSHIFT) (CARRY)

1. Не смотря на то, что ALU может опционально обнулять один из операндов, такие инструкции, как CLR, NEG и TST эту возможность не используют, а используют в качестве операнда Y - регистр констант, равный нулю.

2. Такие инструкции, как CMP, BIT и TST используют блокировку обратной записи результата в операнд-приемник (PL3=1 и PL29=1).

3. Не все операции выглядят рациональными. Например COM использует в качестве операнда Y регистр констант равный флагу C (Y=C), но в самом ALU операнд Y обнуляется.

Последний раз редактировалось Titus; 29.10.2020 в 17:42.

Заодно подоспела вылизанная логическая схема ALU и EALU:

1801VM2-Optimized [ALU & EALU] - rev 43.pdf

Ув. д.г.к. @Titus , очень прошу вас дать мне знать, когда будет готов финальный пакет ваших разборок по этой теме,

поскольку предлагаю разместить копию в библиотеке на сайте архива.

Спасибо.

Сложно ставить точку в теме реверса, оптимизации и понимания работы этих чипов.

Кроме того, @Vslav еще не сфоткал альтернативные ХМ-ки. Так что раньше, чем через год, и не рассчитывай)

hobot(29.10.2020)

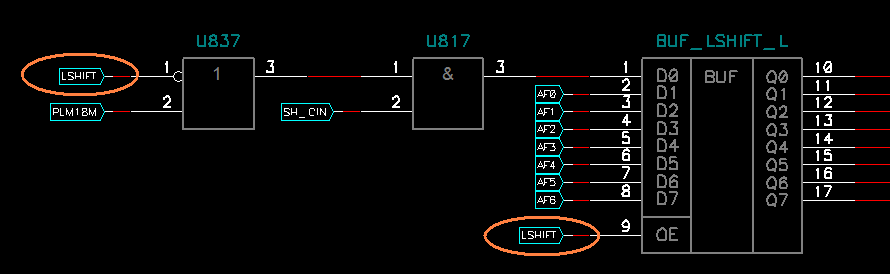

Нашел ошибочку в схеме сдвига. Исправил, но обновлять не буду до будущих обновлений. Все равно никто не интересуется)

@Vslav, посмотрел микропрограмму в ВМ2. Очень хорошо понятна, и расшифровывается без глобального перебора всех комбинаций.

Мало того, перебор всех комбинаций я считаю даже вредным, потому что ты имеешь вход и выход, но не знаешь, почему получился этот выход.

А при логическом анализе микропрограммы, все, как на ладони, чуть ли не с комментариями.

Кроме того, есть шаги микропрограммы, которые не относятся к исполнению элементов инструкций. Например, команда ABORT имеет 10 шагов.

И все эти шаги надо понимать, зачем они и почему.

Эту тему просматривают: 1 (пользователей: 0 , гостей: 1)