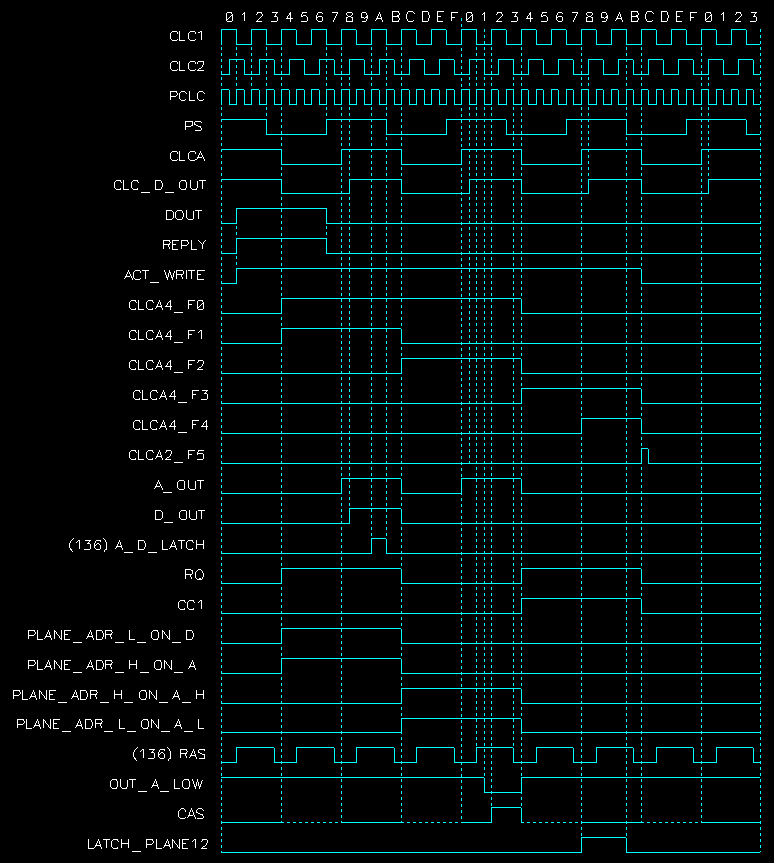

Наименования сигналов:

ACT_WRITE - устанавливается по фронту записи в регистр адреса планов. Сбрасывает по CLCA4_F5 (фаза завершения).

CLCA4_F1 - фаза F1. Адрес планов записывается в видеоконтроллер.

CLCA4_F2 - фаза F2. Чтение данных плана 0 из ОЗУ ПП.

CLCA4_F3 - фаза F3. Чтение данных планов 1 и 2 из видеоконтроллера.

Описание:

Запись в регистр адреса планов (адрес 177010) начинается по переднему фронту DOUT. Одновременно с этим устанавливается сигнал подтверждения записи RPLY. Таким образом, запись в регистр адреса планов имеет для процессора нулевую задержку. Во время активного DOUT данные с шины AD0..AD15 защелкиваются в регистре адреса планов PLANE_ADR.

По отрицательному фронту CLCA (такт 4) устанавливается сигнал RQ.

По положительному фронту CLCA (такт 8) на шину A0..A7 выводится старшая часть регистра адреса планов PLANE_ADR.

Через пол-такта (такт 8.5) на шину D0..D7 выводится младшая часть регистра адреса планов PLANE_ADR.

Еще через полтора такта (такт 10) содержимое шин A0..A7 и D0..D7 защелкивается видеоконтроллером с шин AG0..AG7 и DG0..DG7 в регистрах DC_H, и DC_L, соответственно.

Через один такт (такт 12) шины A0..A7, D0..D7 освобождаются для видеоконтроллера на 4 такта, сигнал RQ переводится в неактивное состояние.

По положительному фронту CLCA начинается процесс чтения данных из ОЗУ ПП в регистр PLANE0_DATA.

Такт 16 - на шину A0..A7 выводится младшая часть адреса планов PLANE_ADR.

Такт 17 - видеоконтроллером устанавливается сигнал RAS, по которому в ОЗУ защелкивается адрес строки (младшая часть адреса планов).

Такт 17.5 - на шину A0..A7 выводится старшая часть адреса планов PLANE_ADR.

Такт 18 - устанавливается сигнал CAS, по которому в ОЗУ защелкивается адрес столбца (старшая часть адреса планов). В течение активного сигнала CAS данные с шины D0..D7 защелкиваются в регистре плана 0 (PLANE0_DATA).

Такт 19.5 - снимается сигнал RAS.

Такт 20 - завершение процесса чтения.

Шины A0..A7 освобождается, сигнал CAS снимается.

Устанавливаются сигналы RQ и CC1.

Такт 24..26 - данные планов 1 и 2, предоставленные видеоконтроллером, защелкиваются с шины D0..D7 в регистре PLANE1_DATA, и с шины A0..A7 в регистре PLANE2_DATA, соответственно.

- - - Добавлено - - -

Не смотря на то, что задержка (latency) записи в регистры октета, планов 1&2, адреса планов нулевая, пропускная способность (throughput) для этих команд значительно ниже.

Подробней можно расписать только зная точную растактовку ВМ2, а также особенности работы контроллеров памяти ПП и ЦП.

Однако, знание нюансов работы контроллеров и процессора, значительно увеличивает возможность оптимизации работы с графикой УКНЦ по скорости.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию