То, о чем 35 лет подряд мечтали миллионы УКНЦ'шников (в лице 5-10 особенно заинтересованных форумчан) свершилось! Загадка записи в раритетные регистры полностью разгадана!

1. Почему запись в раритетные регистры медленнее, чем запись в другие регистры?

2. Происходит ли хоть что-нибудь при записи в раритетные регистры?

Все это вы узнаете в этой серии расследования.

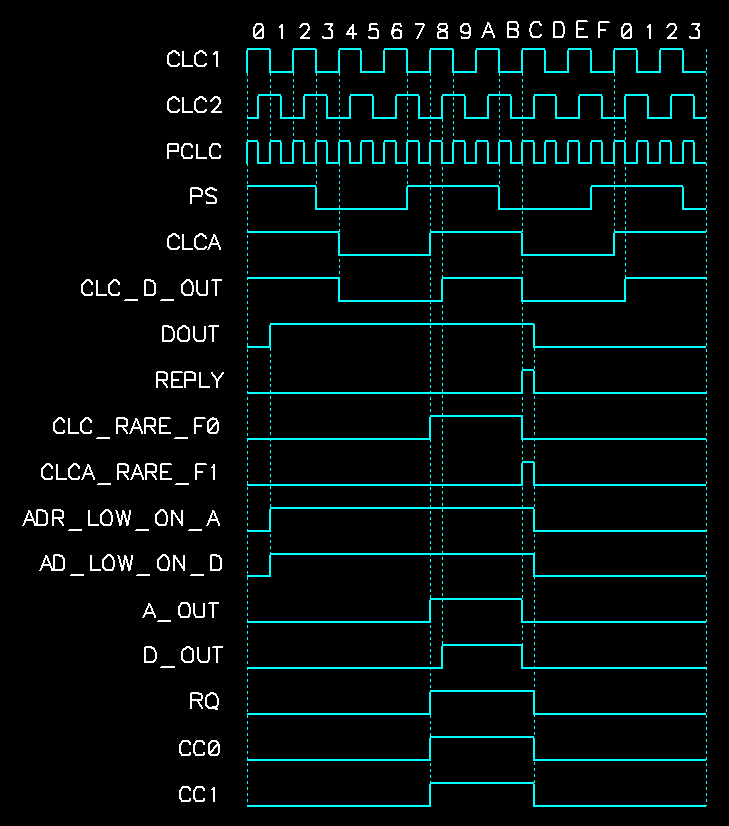

Наименоваия сигналов:

CLC_RARE_F0 - фаза F0. Запись данных на шины D0..D7 и A0..A7. Активна вторую половину цикл CLCA.

CLC_RARE_F1 - фаза F1. Завершение. Активируется по завершению цикла CLCA.

RQ, CC0, CC1 - сигналы обмена с видеоконтроллером.

Описание:

Запись в любой раритетный регистр (RARE_REG, адреса 177030..177057, за исключением регистров 177054 и 177055) начинается по переднему фронту DOUT.

По отрицательному фронту CLCA (такт 4) запускается тактовый автомат.

Во время низкого уровня CLCA (такты 4..7) ничего не происходит (шина находится в пользовании видеоконтроллера).

По положительному фронту CLCA (такт 8) на шину A0..A7 выводится и удерживается младший байт адреса раритетного регистра, защелкнутый в LATCH_ADR по сигналу SYNC. Причем, если запись была словная, то младший бит (A0) обнуляется.

Также устанавливаются сигналы RQ, CC0, CC1.

Через пол-такта (такт 8.5) на шину D0..D7 выводится и удерживается младший байт с шины данных (AD0..AD7).

По окончанию цикла CLCA (такт 12) выдается сигнал RLPY, а так же освобождаются шины A0..A7, D0..D7.

В ответ на сигнал RPLY, процессор снимает сигнал DOUT, после чего снимаются сигналы RQ, CC0, CC1.

Итак, ответы на животрепещущие вопросы:

1. Запись в раритетный регистр медленнее, чем запись в регистр планов из-за того, что сигнал RPLY выдается по окончанию цикла CLCA, что продлевает цикл записи на 2..5 тактов процессора, в зависимости от момента наступления цикла CLCA. Данная задержка выставления сигнала RPLY сделана потому, что при записи в раритетный регистр не предусмотрена буферизация в промежуточном регистре, поэтому данные на шине AD должны удерживаться до окончания цикла передачи данных в видеоконтроллер (CLCA).

2. В видеоконтроллере ХМ1-136 (в отличие от раритетного ХМ1-033) функция записи в раритетный регистр никак не реализована, поэтому на цикл RQ=1, CC0=1, CC1=1 он никак не отвечает.

- - - Добавлено - - -

Я думаю, что комбинацию сигналов RQ, CC0, CC1 можно расшифровать, как Request (о чем всем и так понятно) и Command_Code_0 и Command_Code_1.

Ответить с цитированием

Ответить с цитированием