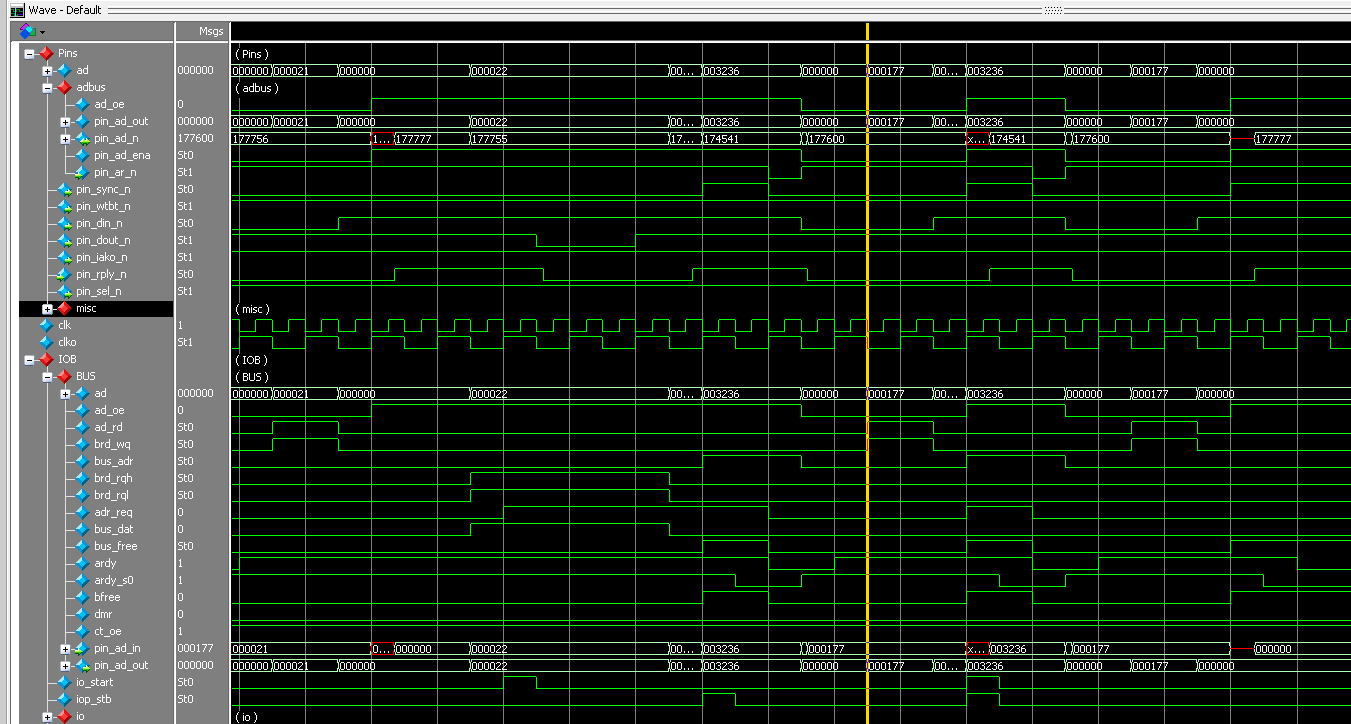

Посмотрел схему ХМ2-001, и заметил, что при чтении данных, сами данные на шину AD выставляются одновременно с сигналом RPLY. Не опасно ли для ВМ2 это делать одновременно? Или же ВМ2 не сразу защелкивает данные с шины по сигналу RPLY, а чуть с задержкой, чтобы данные успели устаканиться?

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию