Отсутствием латчей - вся логика переделана на флип-флопы, а также уменьшено число внутренних фаз с четырех до двух (в моделях для ВМ2). Фазы были нужны для повышения быстродействия физического кристалла, в модели оно особой роли не играет, более того - вредно для синхронной платформы. Теоретически синхронную модель уже можно запихнуть в FPGA (например в проекте БК-0011М для Мистера взяли синхронную модель ВМ1 и, хотя она изначально не предназначалась для реального использования, нормально там работает), но оно выходит не очень оптимально по ресурсам и частоте.

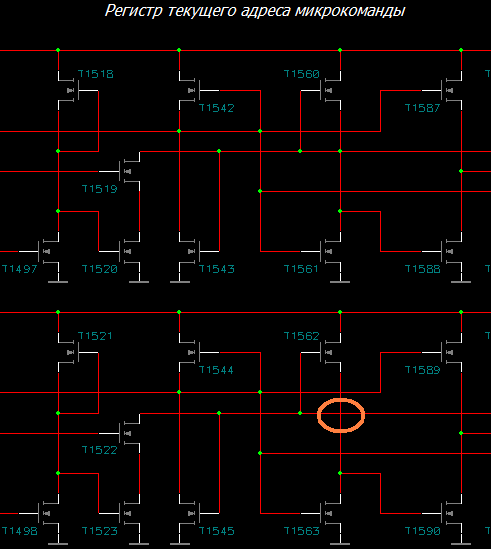

Смотрел на целый блок сразу. Схемотехника n-MOS несложная, после того как сгруппированы транзисторы и нарисован блок - функция понятна. Именно поэтому я не вижу смысла тратить время на перерисовывание в логических компонентах - нет added value, и пропадает автоматическая сверка с топологией - легко налажать и внести ошибки. В моих реверсах я могу мгновенно автоматически сравнить схему с топологией, поэтому у меня вообще не болит голова об ошибках, когда рисую схему - я знаю что при сверке их обязательно увижу и поправлю. Не все любят делать "закат солнца вручную" как ты в реверсах 1515

Мои схемы всегда строго соответствуют топологии. Да, в топологии может быть ошибка - пропущен, скажем, транзистор на фотографии, но логика потом это выявляет (очень хороший пример был в LSI-11). Так что вероятность ошибки собственно реверса небольшая, чаще бывает лажа при переходе в синхрон и потом в оптимизации под FPGA, но именно для этого кейса сохраняется оригинальная модель, в ней обычно ошибок нет (хорошая иллюстрация с последними пофикшенными багами ВМ2) и можно использовать как эталон для отладки.

Ну... Верилог же написан? И даже работает. Значит - пользоваться можно

- - - Добавлено - - -

А вот это как раз тот самый случай когда транзисторная схема демонстрирует схемотехническую особенность.

ADR_EQ - это здоровенный И-НЕ с кучей транзисторов и должен работать быстро. Поэтому в подтяжку поставили не просто depletion load, а специальный транзистор T6636 - он успевает быстро зарядить всю эту относительно большую емкость цепи ADR_EQ. Я думаю там в нем еще и некоторое легирование канала есть - T6636 вероятнее всего дополнительно обеспечивает слабенький pull-up для ADR_EQ. Легирование мы на фотографии не увидим, но логика работы всего этого блока понятна и так - компаратор адреса. ACMP_EN обычно сидит в нуле, ADR_EQ - высокий, T6636 открыт, емкость цепи заряжена. При сравнении адреса - ACMP_EN переходит в высокий, T6636 закрыт (возможен слабенький pull-up) и ADR_EQ уже может разрядится в ноль каким-либо разрядом компаратора. ACMP_EN еще и подфильтровывает эти разряды - чтобы срабатывало именно в определенный момент, когда все переходные процессы в XOR-aх завершились.

Ответить с цитированием

Ответить с цитированием