Скрытый текст

Даров!

Откопал в закромах задумки по своему "плюсе"Может сгодится тебе или кому еще.

Если интересно выложу сам файл для Logism или в почту зашлю. Можно пощелкать на симуляции, посмотреть как оно работает.

Если кратко, комп планировался по "memory map", как некий симбиоз ZX+MSX, я использовал наработки Кота по Химере.

Процессора 2 - Z80 и Z180, оба могли работать как основной. Z180 чуток не совместим с Z80, поэтому в режиме ZX, мог использоваться как акселератор для расчетов на 28-32МГц, разделяя с Z80 страницы теневой памяти на SRAM.

В 4 банках по 16КБ, может подставляется до 4МБ SRAM в каждый, с автоматическим контролем записи и чтения, как в основную память на DRAM так и в теневую . Штатно и скромно планировалось по 32КБ SRAM, в каждый банк,

дальше можно расширять, через слоты на плате.

Наращивать, память в CPU3 смысла особо никого, кроме диска ее мало кто использует. Да и маппер DRAM во все банки не мне зашел. Поэтому пошел другим путем.

Т.е. можно вертеть памятью как хочешь, на скрине пример с RAM-5. Например можно еще добавить 2 буфера 74als244/АП5 на шины памяти и бит для их переключения и заставить видео сканер ZX читать уже с теневого ОЗУ.

Видяха планировалась пентагон/фирма. По типу твоей .

Для контроля памяти используется порт #ADF7, в каноническом изложении Кота, это порт старших адресов ОЗУ в СPU2, до 1Gb, накой ляд столько 8 битке мне не ведомо

Вообще, порт можно выбрать и другой.

Для переключения теневых страниц в банках- порты #AxF7.

Для управления ROM/RAM в CPU0 используется #1FFD и #EDF7.

У него на форуме можно почитать, подробнее.

Ну и из Химеры, планировалось взять еще многое.

Вообщем плюсов от такого расклада достаточно много, можно иметь огромный и уже готовый по меркам ZX ,буфер например в теневой RAM-5, кидать в него графику, откуда угодно, потом перекинуть его часть, уже в RAM-5 основной памяти.

не портя до этого основную память. Можно поиграться с многозадачностью, и всякие СPM и UZIXы.

Теоретически проц, может работать в теневом ОЗУ без WAITов на 14MГц .

При желании можно отключалючить сразу 2 банка и сделать видеорежим с Sam Сoupe, который хочет 24КБ, при этом основная память не пострадает.

Из минусов, куча корпусов и желательно 74F/1531 или CPLD. Может соберусь и сделаю платку для апгрейда своего Феникса . Теоретически отрезать только CS_RAM и WE/ + 1 элемент ИЛИ, RDROM/. Ну и питание снять с микрух на плате, которые

отвечают, за менеджент памяти, чтоб разгузить шину.

В черновике могут быть ошибки, тема старая, поправил как мог.

Вот такой был амбициозный прожектЖелезо без софта мертвое(с)

Удачи.

[свернуть]

Даров.

Вот часть, реализовано управление всеми банками памяти. В каждом банке может быть свой модуль памяти.

Порты взяты химеровские, но не совсем по прямому назначению, но не суть.Пусть будет как пример.

Реализовано расширенное управление памятью в СPU0 по химере.

Полное управление чтением/записью в CPU0, в CPU1 есть ограничение -нельзя сделать теневую страницу только на запись, CPU2,3 -упрощенное управление.Можно только исключать чтение/запись в основную память и вместо нее подключать страницы теневой памяти.

Например, загружаем в теневые страницы CPU0 графику , включаем на чтение.

В основной основной памяти CPU0 делаем наш буфер, хоть все 16КБ, памяти не жалко. Там у нас бесполезный ROM, раньше был.

Включаем основную память только на запись.

Теперь процессор будет автоматически читать из теневой, а писать в основную. Все в рамках только $0000-3fff.

Например в теневой памяти CPU2 или 3, есть уже развернутая процедура переброски буфера в экран ldi, ldi ..ldi , памяти не жалко у нас ее есть в теневой, включаем -перебрасываем в экран из CPU0. Отключаем.

Можем сделать сразу 2 копии буфера, включив память на запись. И основную, и теневую. И чтобы не восстанавливать фон, сразу включить копию. Этот случай частный конечно.

Но основную идею, с теневой памятью я надеюсь донес.

Реализовано отключение основной памяти с 0000 по 5FFF. Теперь можно сделать режим sam coupe 16 цветов или любой другой какой поместится в 24KБ. опять за счет ПЗУ и экрана. В этом случае 2 варианта.

Либо использовать внешнюю память видеокарты (опыт у тебя есть)либо теневую .

Вот в краце все. Надеюсь, когда нибудь увидим такой компик.Если народу будет будет интересно, в прицепе можно сделать карточку под краевой разъем Фени, в CPLD, разъем все одно без дела в основном, комп придется чуток порезать, но не много и аккуратно ножки у микросхем, раза 3-4

. до кучи и расширитель слотов сделать..

На гугл диске логизм, библиотеки, схемка . для логизма нужна java.

http://www.cburch.com/logisim/ru/index.html

Удачи.

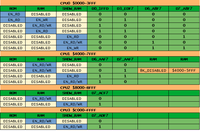

Пример порта управления теневой памяти

#A8F7

D0 - CPU0 A14'RAM

D1 - CPU0 A15'RAM

D2 - CPU0 A16'RAM

D3 - CPU0 A17'RAM

D4 - CPU0 A18'RAM

D5 - CPU0 A19'RAM

D6 - CTRL

D7 - CTRL

|D0#1FFD|D3 r/wCPU0 MANAGETMENT - биты определяют режим работы и тип памяти в окне CPU0

|_0 _____|_0 - rdROM - в окне CPU0 доступно ПЗУ только на чтение

|_0 _____|_1 - rdROM & wrRAM - в окне CPU0 доступно одновременно ПЗУ на чтение и ОЗУ на запись

|_1 _____|_0 - r/wRAM - в окне CPU0 доступно ОЗУ на чтение и запись

|_1 _____|_1 - rdRAM - в окне CPU0 доступно ОЗУ только на чтение

http://www.cburch.com/logisim/ru/index.html

https://drive.google.com/drive/folde...Fk?usp=sharing

Ответить с цитированием

Ответить с цитированием