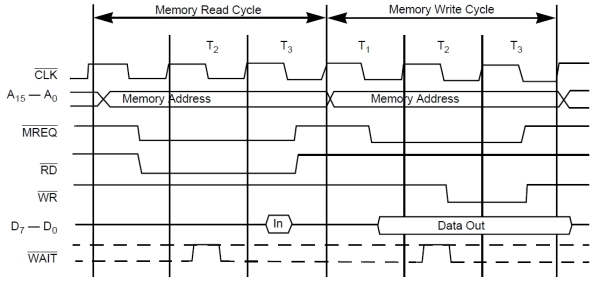

Полагаю, многим спектрумистам знакомы подобные картинки:

...происхождением из фирменных мануалов и даташитов, которые кочуют с сайта на сайт.

При этом везде подробно рассмотрены и описаны только трёхтактовые (не считая wait) машинные циклы чтения/записи, в том числе и в фирменных документах. Но циклы чтения бывают также четырёхтактовые, а циклы записи - пятитактовые (пример команды, в которой есть циклы всех размеров - "ex (sp),hl"). Причём дополнительные такты - явно не wait, а вычисления уже после чтения или записи. Что же точно происходит с шинными сигналами в это время? Смущает, что в отдельные одно-двухтактовые внутренние машциклы эти дополнительные такты в доках не выделяют.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию