Данный проект представляет собой FPGA-конструктор, с помощью которого можно собрать в железе микро-ЭВМ ДВК-1, 2, 3 и Электроника-60, а также ЭВМ Электроника-79.

Проект является модульным - состоит из кучки модулей, объединенных шиной wishbone. В основе схемы лежит соединительная плата topboard (аналог МПИ-корзины реальной ЭВМ), к которой подключается одна процессорная плата и набор периферийных устройств.

В данный момент реализованы следующие процессорные платы:

МС1201.01 на процессоре 1801ВМ1 - на ней основаны ДВК-1 и ДВК-2

МС1201.02 на процессоре 1801ВМ2 - ДВК-3

МС1260 на процессоре М2 (DEC LSI-11) - Электроника-60

МС1280 на процессоре М4 (DEC LSI-11M) - вот тут я даже не знаю, были ли какие-то ЭВМ на ее основе.

PDP2011 на процессоре PDP-11/70 - это чисто синтетический процессор, аналогом 11/70 была эвм Элекроника-79.

В комплекте имеются следующие устройства:

- Контроллер ИРПС (модуль wbc_uart от VSLAV) по адресу 177650 для связи с консольным терминалом

- Дополнительный контроллер ИРПС по адресу 176500 для связи с внешним миром (LS:, XL)

- Контроллер КСМ (контроллер символьного монитора) - VT52-совместимый текстовый терминал

- Контроллер КГД (контроллер графического дисплея)

- Контроллер RK11 (RK) с подключенными у нему 8 дисками RK05

- Контроллер RK611 (DM) с подключенными у нему 8 дисками RK07

- Контроллер RH70 (DB) с подключнными к нему 8 дисками RP06

- Контроллер HDD RD50C (DW) в варианте ДВК с подключенным к нему виртуальным HDD объемом 64 Мб.

- Контроллер RX11 (DX) с подключенными к нему двумя дисководами RX01 (наш аналог - ГМД70)

- Контроллер ГМД двойной плотности (MY) с подключенными к нему двумя двухдисковыми дисководами НГМД-6121.

- Контроллер динамической памяти DRAM объемом 64 Kб

- ПЗУ эмулятора пульта/загрузчика, аналогичное DEC M9312

- ПЗУ пользователя для хранения резидентных программ (обычно basic или focal), размещается по адресам 140000-157777

Состав собираемой ЭВМ и ее параметры определяются в едином конфигурационном файле config.v.

Первый вариант проекта был сделан на процессорном ядре 1801ВМ2 от уважаемого VSLAV, и создавался мной в силу жизненной необходимости - как замена окончательно сдохшему контроллеру, который управлял испытательным стендом у нас в лаборатории. Плата с лета 2020 года трудится практически каждый рабочий день, все основные глюки за это время выловили и исправили. Прошу заметить, что этот проект разрабатывался не как игрушка-эмулятор древней ЭВМ, а именно под конкретные производственные задачи. В силу этого внимание уделялось функциональности устройства, а не абсолютой точности эмуляции оригинального железа.

В результате получилось функционально законченное устройство, представляющее собой одноплатный вариант древних советских персональных ЭВМ. Достаточно подключить к FPGA клавиатуру, VGA-монитор и SD-карту - и ЭВМ готова.

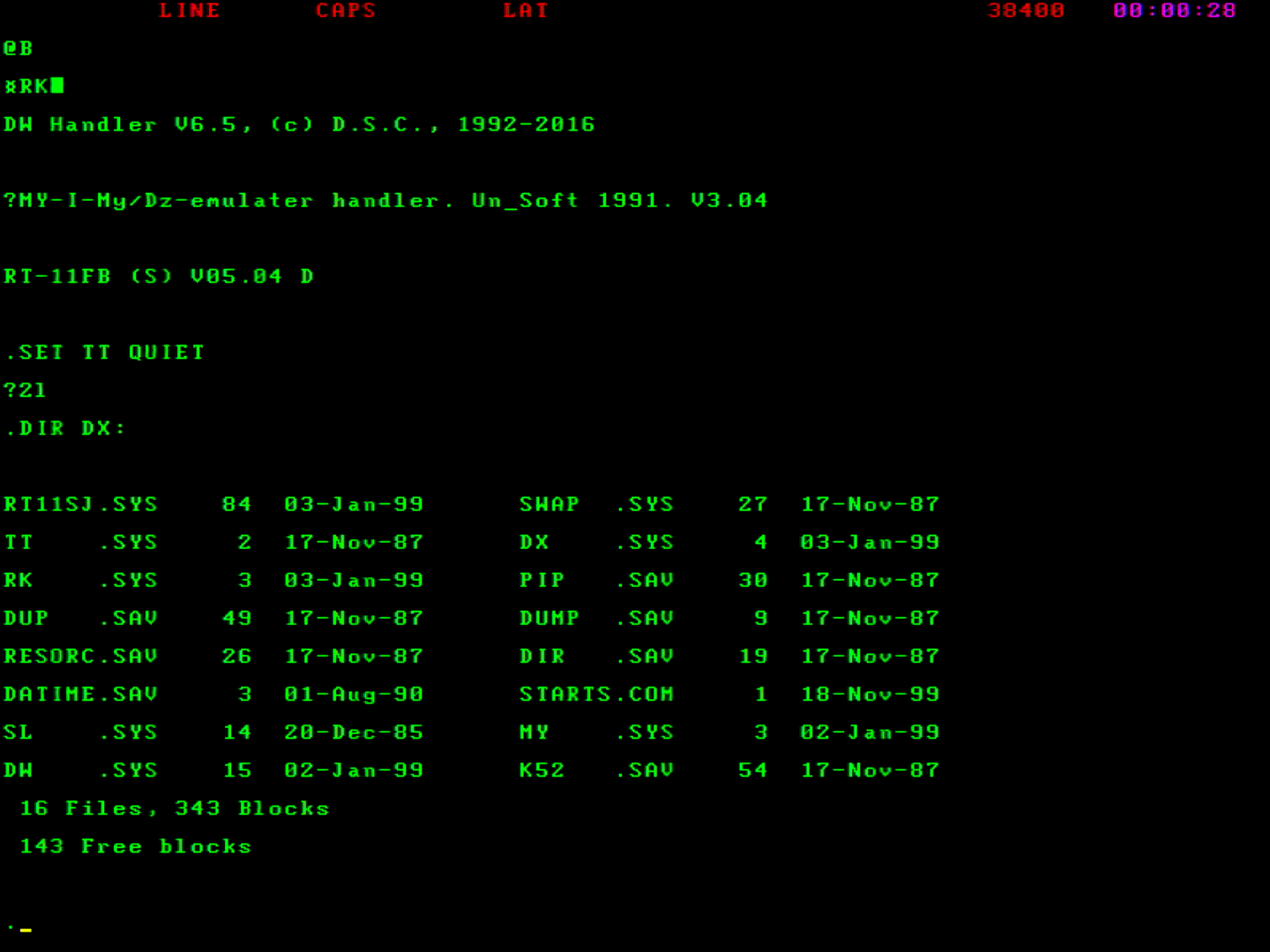

Пример загрузки RT-11

[свернуть]

Пример запуска системных тестов

[свернуть]

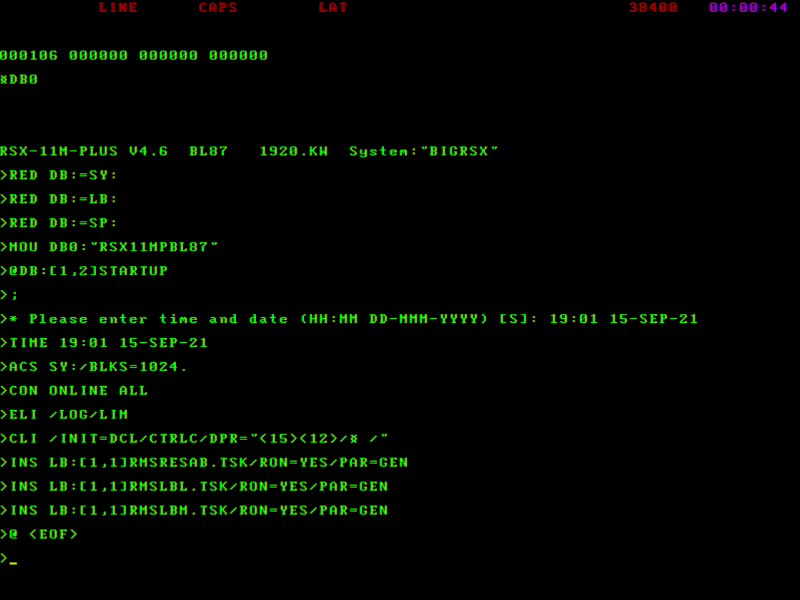

Пример загрузки RSX-11M-PLUS

[свернуть]

Все дисковые контроллеры используют единственную карту памяти SD для хранения образов своих дисков. В проект входят утилиты для извлечения образов с SD-карты и записи их обратно на карту. Кроме того, в проект входит пример готового банка дисков, готовый для поблочной записи на SD-карту - его я внес в проект для облегчения первоначального запуска и отладки на конкретной FPGA-плате.

Можно добавлять на шину свои собственные модули - это делается достаточно легко. У меня, например, на шине присутствуют модули ЦАП, АЦП и набор дискретных портов для стыковки со стендом. К проекту прилагается краткое руководство по созданию собственных модулей build-own-modules.pdf. То есть этот проект можно использовать не только для сборки законченной микро-ЭВМ, но и как основу для замены физически устаревших управляющих контроллеров, основанных на какой-либо из поддерживаемых процессорных плат.

В каталоге doc/ проекта лежит файл с документацией main-manual.pdf, и я крайне рекомендую ходя бы поверхностно с ним ознакомится. В нем подробно описывается работа каждого периферийного модуля и содержатся ответы на многие вопросы, которые потенциально могут возникнуть при запуске проекта на конкретной плате.

Проект портирован на многие отладочные платы, в основном основанные на FPGA серии Cyclone-4 фирмы Altera. В полной конфигурации проект вполне помещается в чип EP4CE10, что позволяет использовать относительно недорогие китайские платы. В данный момент имеются порты на следующие платы:

A-E115FB

A-ESTF v2

Alinx AX4010

QMDAZZ rz301

QMTECH E55

Sipeed TANG Primer

Нетрудно портировать схему на другие платы - главное, чтобы хватило ресурсов. Никаких особенностей серии Cyclone 4 проект не использует, из фирменных мегафункций использованы только PLL и Altsyncram.

Проект живет в репозитории https://github.com/forth32/dvk-fpga.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию