Сообщение от

andrews

у чипов DC год неделя, только британцы по своему выеживаются

Вообще не понял, на что этот ответ)

- - - Добавлено - - -

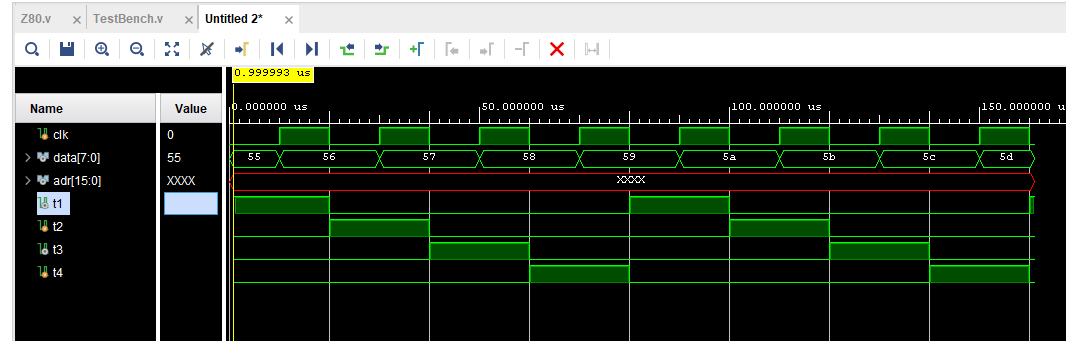

Еще несколько вопросов по vivad'е:

1. Как компилировать проект без запуска симуляции, чтобы просто проверить на ошибки?

2. Можно ли счетчику (регистру, вход которого соединен с выходом), не задавать никакого начального значения? Это используется в Z80, например, для выбора набора регистров, общий набор/альтернативный. Там абсолютно все равно, какой набор включен при старте процессора, т.к. наборы равнозначные. В vivad'е если такому регистру не установить начальное значение, то он всегда будет в неопределенном состоянии. Можно ли, чтобы при запуски в нем просто было случайное значение любое?

3. По поводу встроенных в ПЛИС модулей памяти. Когда я пишу вот такой простейший модуль памяти:

Код:

module ram(

input clk, // Тактовый сигнал для синхронного чтения

input [7:0] data_in, // Шина данных (8 бит) (ввод)

output reg [7:0] data_out, // Шина данных (8 бит) (вывод)

input [15:0] adr, // Шина адреса (16 бит)

input mreq, // Запрос доступа к памяти (на шине адреса установлен адрес для доступа к памяти)

// input rd, // Запрос чтения памяти

input wr // Запрос записи в память

);

reg [7:0] ram [0:15]; // ОЗУ на 16 байт

initial $readmemh("ram_image.mem", ram); // Загрузить дамп данных из файла в память

always @(negedge clk) // Активность по отрицательному фронту clk

begin

if (wr & mreq) // Если активны сигналы WR (запись) и MREQ (запрос памяти),

ram[adr] <= data_in; // то записать байт в память по адресу adr

else // Всегда, когда не записи, идет чтение памяти

data_out <= ram[adr]; // то выдать байт из памяти по адресу adr на выходной регистр шины данных

end

endmodule

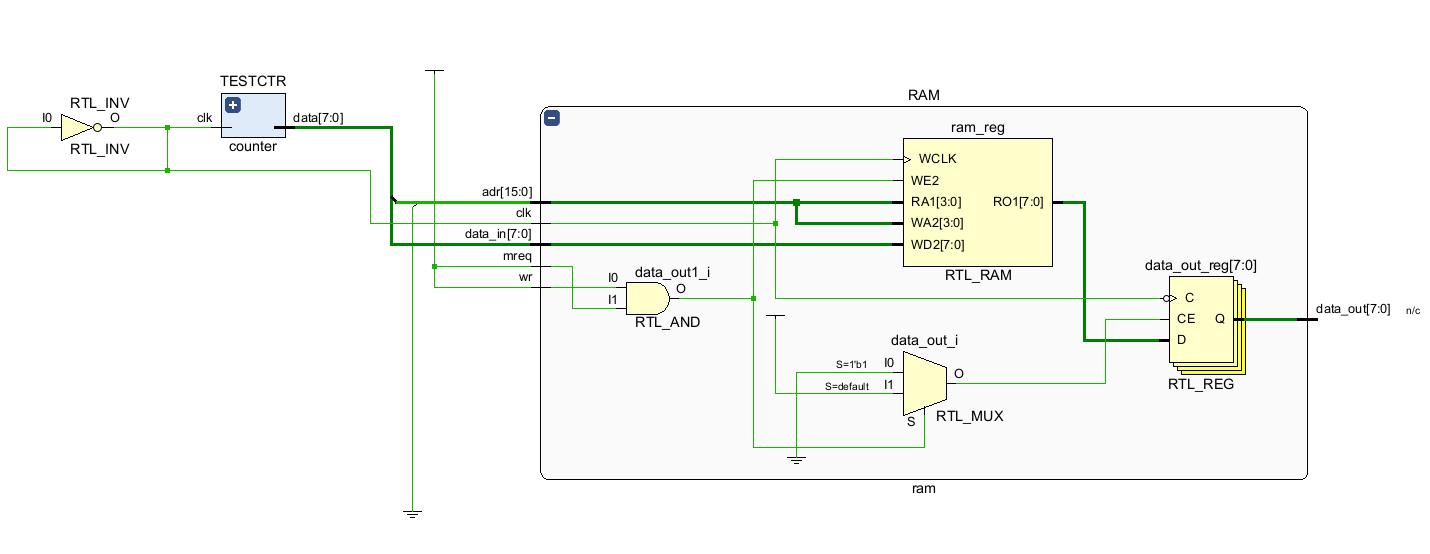

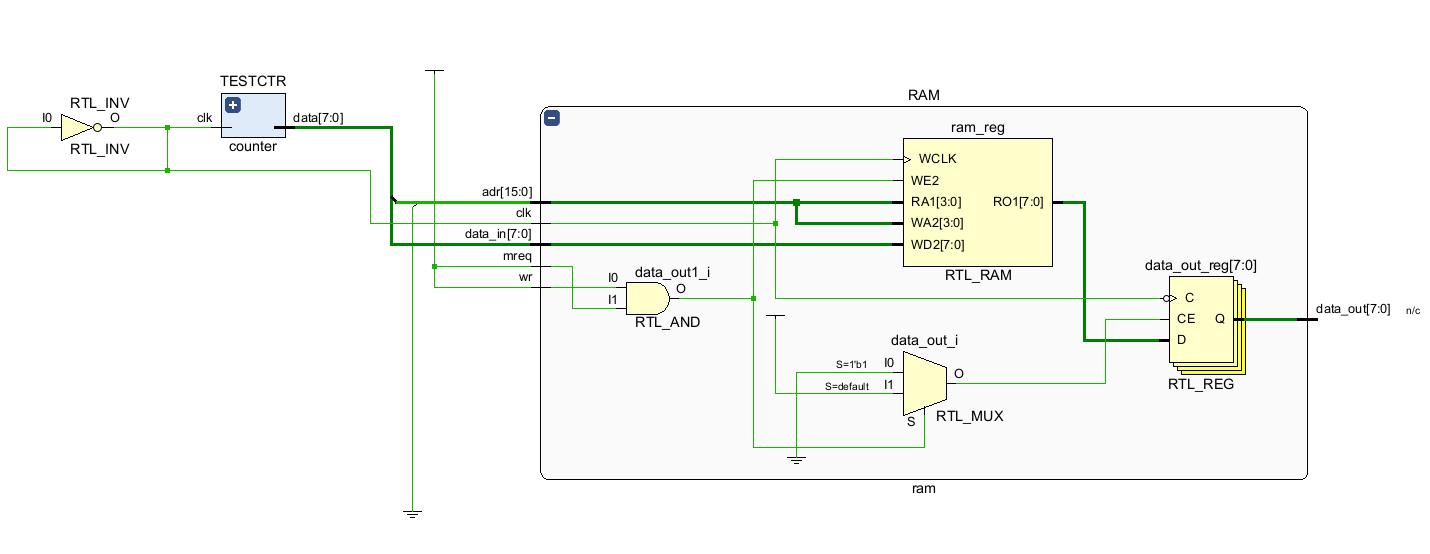

Из него получается вот такая схема:

Скрытый текст

[свернуть]

Меня смущает, что RTL_RAM тактируется фронтом на входе WCLK, а сгенерированный регистр RTL_REG тактируется (но спадом). Тогда по логике, память работает по фронту CLK, а выходной регистр по спаду. Но это не соответствует моему коду. Почему так? Если у встроенной памяти есть на выходе защелка, зачем компилятор ставит дополнительную (RTL_REG)? И зачем тут вообще этот RTL_MUX?

- - - Добавлено - - -

4. Да, и как запомнить положение и соотношение окон в проекте? А то каждый раз при запуске симуляции все сьезжает.

5. И наконец снова не нарадуюсь, на сколько Vivado дружественней, чем ModelSim.

6. Как настроить, чтобы при запуске симуляции она запускалась сразу на какое-то количество временных отрезков заданное мною, чтобы я сразу видел результат в окне. Да и как сделать, чтобы окно симулятора запомнило, какие сигналы я хочу смотреть, какие надо скрыть?

Ответить с цитированием

Ответить с цитированием