Сообщение от

HardWareMan

Осмелюсь предположить, как и в случае с ВМ80, регистр А и тем более флаги - особые.

В случае Z80 как раз AF хранится в общем регистровом файле, а флаги кэшируются непосредственно перед выполнением очередной команды.

Но думаю, что задумка была именно такая, подальше разнести момент обмена AF (такт T1) и загрузка AF по умолчанию в начале следующей команды (такт T2).

Думаю, если перенести EX AF,AF' с T1 на T2, все работало бы так же прекрасно.

Впрочем, если хотелось так заранее все сделать, никто не мешал авторам и EXX сделать в T1, а не T2.

В общем, как сделали, так и сделали)

- - - Добавлено - - -

Кстати, поговорил с ребятами с эмураши (nukeykt), они рассказали, как реверсили Z80.

Сперва NMOS в августе 2022, затем сейчас CMOS уже почти сделали (примерно месяц на реверс процессора!).

Схема на уровне вентилей перегонялась сперва на Си, затем на Verilog.

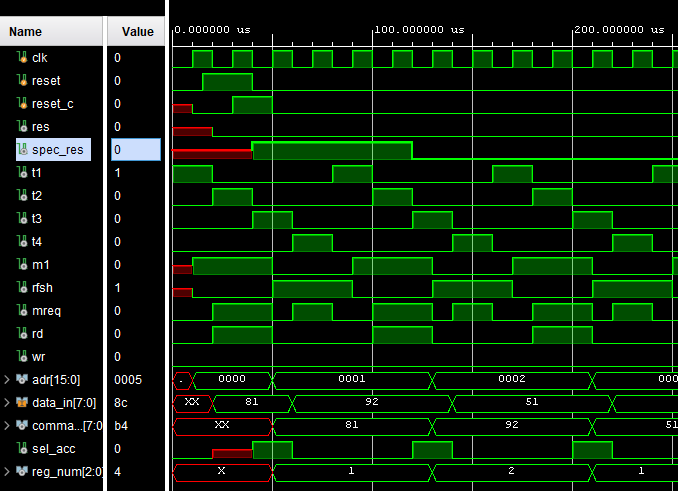

Т.к. версия оставалась асинхронной, то делался дополнительный мастер-клок (MCLK), в несколько раз превышающий CLK, и с помощью него эмулировались латчи примерно так, как я уже писал выше:

Код:

always @(posedge MCLK)

begin

if (CLK)

x <= a;

end

Плюс этого подхода, что схема фактически оставалась оригинальной, без вмешательств. Меньше поле для косяков, когда ручками переделываешь на синхронный дизайн.

Минус - завышенная тактовая, что приводит к дополнительной трате ресурсов.

Кроме того, такой подход не требует детального понимания работы схемы. Фактически это клонирование и симуляция.

Вот так понял я из общения с ними.

- - - Добавлено - - -

Я люблю максимально все оптимизировать, поэтому без глобального разбирательства в принципах работы схемы и переделывания на синхронный дизайн исходя из этого не обойтись.

Но это да, значительно затратнее по времени и всему остальному.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию