AF читается всегда целиком 16 бит. А записываться может по частям..

Там две 8-битных шины, каждая из которых может работать отдельно друг от друга. Кроме того, обе эти шины могут обьединяться (пробрасывается мост с HBUS на LBUS). Причем, практически все операции как раз и проходят в режиме обьедененных шин, т.к. работа идет с 8 битами.

- - - Добавлено - - -

Есть возможность одновременного чтения/записи в старшую/младшую часть регистров. Единственное ограничение, это должен быть один и тот же регистр. Допустим, A читаем, F пишем. Другой вопрос, используется ли это, я еще не проверял.

Что касается всего регистрового файла, то, как я уже писал выше, он состоит из двух матриц. В одной из них почти все регистры, в другой PC и IR. И между ними тоже может образовываться мост. Вот в эти две части регистрового файла можно писать и читать одновременно разные регистры. Например, PC читается, и в это же время какой-то другой регистр тоже читается или записывается.

- - - Добавлено - - -

Несколько названий сохранились от проекта Z80 Explorer, другие же я обозвал сам по их назначению. Впрочем, пришлось переименовать шины, названные в Z80 Explorer VBUS и UBUS в LBUS и HBUS, т.к. это лучше соответствовало их назначению.

- - - Добавлено - - -

Там много промежуточных защелок, в которых все это хранится. Как на входе АЛУ, так и на выходе.

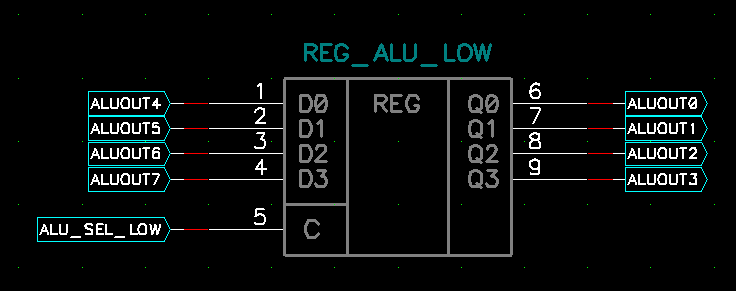

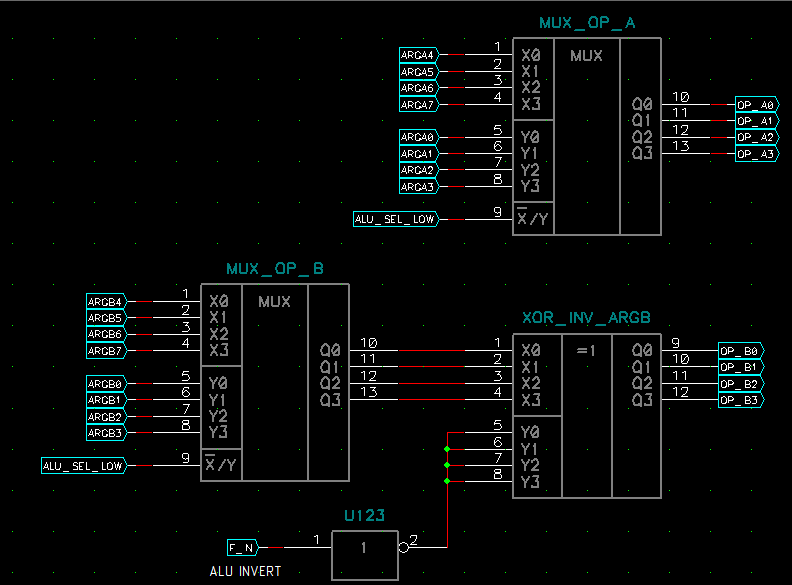

Вот кусочки схемы:

Выход

Вход

- - - Добавлено - - -

Я занимаюсь для того, чтобы понять нюансы его работы) Без этого точный эмулятор не напишешь. А я же эмуляторщик)

Ничего не заканчивал связанного с электроникой. Я программист.

Но я уже столько отреверсил чипов (для УКНЦ), что для меня это уже не особо сложная задача, просто кропотливая. Что делать, если никто не сделал, а хочется)

Многие реверсят до транзисторного вида, иногда даже не причесывая, и либо засовывают в FPGA, либо симулируют, как в Z80 Explorer. Но это не дает информации о нюансах работы. Да и плавающие состояния тут можно упустить. Единственный вариант, на мой взгляд, познать всю суть работы процессора - это построение причесанной и понятой транзисторной схемы, а по ней логической.

- - - Добавлено - - -

Вот чего мне менее всего интересно, это сидеть перерисовывать слои с кристалла.

Идеально, если уже есть потранзисторная схема, пусть даже просто в виде списка транзисторов и соединений. С чего я и начал реверс Z80, собственно.

- - - Добавлено - - -

На счет этого теста.

Думаю, что причина в том же - обилие динамических защелок в блоке формирования флагов.

Впрочем, их много в принципе в этом микропроцессоре. Но большинство из них тактируются CLK, и на частоте работы процессора работают как статические. А вот в блоке формирования флагов много наворотов, в том числе и с динамическими защелками, тактируемыми как придется. Так что вполне возможно, что утечки можно добиться. Надо проанализировать их работу на досуге, просто пока до них не дошел, только до флага S, о котором рассказывал выше.

Замечу, никто еще не вызвался проверить мое предположение на NMOS реале.

- - - Добавлено - - -

Немного о блоке формирования флагов:

S - флаг знака самый простой, в него просто копируется 7-бит результата работы АЛУ.

Z - флаг нуля почти такой же простой, формируется, если результат работы АЛУ равен 0. Однако там есть дополнительная цепь установки, сброса, обратной связи. Зачем она нужна, еще не разбирался.

N - флаг сложения/вычитания. Именно по этому флагу АЛУ знает, что нужно делать, складывать или вычитать (то же сложение, но второй аргумент инвертируется). Крайне интересно, что команды относительного условного перехода (и не только), использующие АЛУ для получения эффективного адреса, кешируют во нутренний кеш этого флага предыдущее состояние флага S(!). С чего бы это? Еще не разбирался. Должно быть, чтобы понять, вычитать смещение или прибавлять, в зависимости от знака смещения.

C - флаг переноса. Работает в целом весьма документированно, за исключением того, что для команд AND, CCF, SCF в него копируется инвертированное значение флага H(!) (полупереноса). Видимо, таким образом команда CCF инвертирует флаг C, пропуская его через полуперенос.

H - флаг полупереноса один из самых навороченных. Единственное, что пока могу сказать, он всегда изменяется для всех команд, которые влиют хотя бы на какие-то флаги. Т.е. у него нет кеша предыдущего его значения.

PV - флаг четности/переполнения - пока не разбирался.

Ответить с цитированием

Ответить с цитированием