Опять лирическое отступление на тему ПЛИС.

Как устроены у современных ПЛИС RS-входы у D-триггеров? Эти входы тоже синхронны с CLK, либо же вход D работает синхронно, а входы RS асинхронно?

Опять лирическое отступление на тему ПЛИС.

Как устроены у современных ПЛИС RS-входы у D-триггеров? Эти входы тоже синхронны с CLK, либо же вход D работает синхронно, а входы RS асинхронно?

Xilinx 7 семейство Физическая реализация

Триггеры:

FDCE Primitive: D Flip-Flop with Clock Enable and Asynchronous Clear

FDPE Primitive: D Flip-Flop with Clock Enable and Asynchronous Preset

FDRE Primitive: D Flip-Flop with Clock Enable and Synchronous Reset

FDSE Primitive: D Flip-Flop with Clock Enable and Synchronous Set

Защёлки (не рекомендуется использовать, но они есть в наличии).

LDCE Primitive: Transparent Data Latch with Asynchronous Clear and Gate Enable

LDPE Primitive: Transparent Data Latch with Asynchronous Preset and Gate Enable

Сиё взято из документа: UG768 "Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs UG768 (v14.7) October 2, 2013"

Последний раз редактировалось AlexG; 11.09.2024 в 12:09.

Titus(11.09.2024)

есть универсальный приметив ТРИГГЕР. в зависимости от того как он сконфигурён (при загрузке плисы) тем он и будет.Пример: есть 100 триггеров всего из них одновременно можно сделать

1 FDCE и 99 FDRE

а можно

по 25 штук каждого.

Titus(11.09.2024)

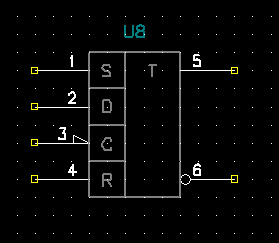

Интересно, как мне обозначать в схеме триггеры, у которых не только D синхронный, но и RS.

Потому что сейчас триггеры с асинхронным RS обозначаются так:

ХЗ. Наверно для синхронного : D C R входы объединять в одном прямоугольнике, а если асинхронный R вход - то примерно как в 155ТМ2 (в отдельном прямоугольнике).

ПС: к сожалению (для нас) и к радости (инженеров) в плисах нет триггеров с R и S входами одновременно. и всегда есть D и C.

Последний раз редактировалось AlexG; 11.09.2024 в 13:46.

Titus(11.09.2024)

Выше перечислен базис примитивов. На основе оных и доп. логики формируются все остальные "интимные фантазии" инженера... с той или иной точностью поведения

ПС: на практике в 99,9999% случаях ни кто не заморачивается с использованием примитивов напрямую (за исключением специализированных примитивов). Просто пишется описание требуемого поведения схемы на языке HDL - если написано реализуемая схема - то получаем прошивку, а если нет - то упрощаем описание...

Применение примитивов это как Асм вставки в СИ языке.

Последний раз редактировалось AlexG; 11.09.2024 в 13:52.

Ок. Значит буду писать на Verilog с расчетом, что все триггеры синхронные, и RS входы тоже синхронные. А трассировщик сам уже разберется. Естественно, прослежу, чтобы R и S не могли устанавливаться одновременно.

AlexG(11.09.2024)

Titus, а почему Z80 опкод защёлкивает по спаду такта, а данные (аргументы и прочее) по фронту (так же, как и ВМ80)? С чем связано такие различие в циклах внешней шины?

Эту тему просматривают: 1 (пользователей: 0 , гостей: 1)