С любовью к вам, Yandex.Direct

Размещение рекламы на форуме способствует его дальнейшему развитию

Ну раз топик превратился в "помоги Титусу освоить верилог" добавлю от себя:

для простейшей симуляции можно вообще всё делать без always блоков, тупо соединяя вентили нетлистом. Сейчас сразу набегут сторонники православного синтеза, но таки наша утилита Deroute именно такой верилог и выгружает (модульный) - и запихать always блоки внутри DFF примитивов тоже можно.

Пример модульного ядра SM83 из DMG SoC:

https://github.com/emu-russia/dmgcpu...HDL/sm83/Top.v

Оно вполне себе работает в икарусе и этого обычно достаточно для "понимания".

P.S. Ещё рекомендую изучить гига-лики от Nintendo (лежат в открытом доступе как ни странно на archive.org) и посмотреть как делалось "по-взрослому", например исходники RСP от Nintendo 64. Ещё можно полазить по OpenCores и приуныть немного, хотя тоже полезно.

Последний раз редактировалось org; 18.10.2024 в 23:27.

Хоть я и начинающий вериложник, но у меня задача сразу делать красиво и правильно. Я имею в виду Z80. Только синхронная схема, все оптимально и красиво чтобы было.

- - - Добавлено - - -

Приуныть от чего?

- - - Добавлено - - -

Лучше не выражаться сленгом, а давать конкретные ссылки с уточнениями.

Может так получиться что когда начнешь делать красиво и правильно, то что-то получится, но уже не z80.

Ссылки которые можно давать я даю, которые нельзя я не даю, leak - сам понимаешь, гугли.

На OpenCores много ядер и другого железа на верилоге, есть кстати и z80 сделанный по мотивам чипа, так что как минимум можно приуныть что уже всё сделано до нас.

https://opencores.org/projects/a-z80

Я всегда стараюсь сохранить максимальную аутентичность оригиналу. Но, естественно, моделировать потранзисторную схему на Verilog'е.

Раз правила хорошего тона для ПЛИС - это логика плюс триггеры по фронту, шины без Z состояний, значит перевожу Z80 в этот формат.

- - - Добавлено - - -

Эти видел.

Нет, до меня еще никто не делал логическую модель по точному реверсу.

А даже если бы и сделали, мне все равно интересно сделать свою конфетку. Может она будет компактнее и быстрее. И точнее.

- - - Добавлено - - -

Вообще, я смотрю, логическую схему с триггерами перевести на Verilog вообще не сложно. Гораздо проще, чем писать программный эмулятор.

Но пока что в схеме есть узкие места, например, триггеры, работающие и по фронту и по спаду такта одновременно. Вот это надо сперва по умному переделать, а потом описывать.

- - - Добавлено - - -

Для случая, когда длительность импульса ресета очень короткая (меньше 1 такта), есть участки схемы, которые поведут себя весьма косячно.

Внутренний импульс RES всегда выравнивается на границу такта, поэтому самый короткий внешний импульс все равно будет равен 1 такту внутреннего RES.

Смотрим на такой фрагмент схемы:

Как видим, если RES равен 1 такту и совпал по времени с T3, то сначала RS-триггер перейдет в третье состояние, когда оба выхода равны нулю. А после одновременного снятия T3 и RES перейдет в неопределенное состояние вообще. Думаю, что с большей вероятностью пересилит правое плечо, т.к. там больше емкость затворов подключенных к нему транзисторов. Но все же.

AlexG(19.10.2024)

Я так понял, что чтобы в режиме Schematic все не перепутывалось друг с другом, надо помельче дробить модули?

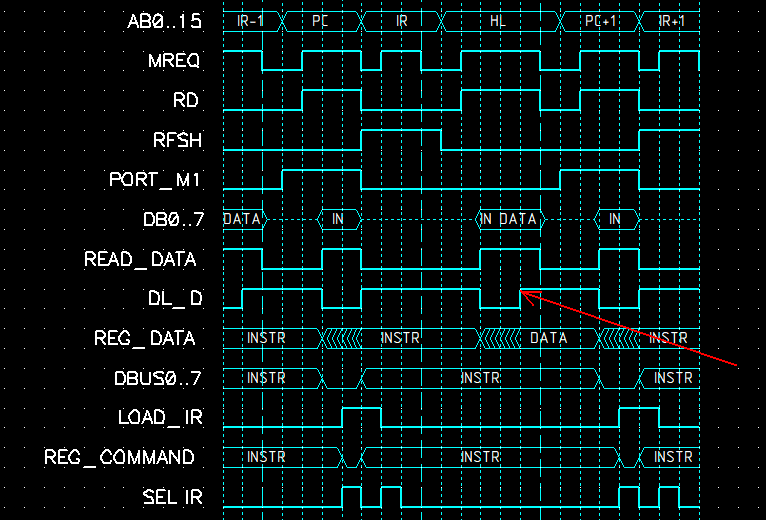

Еще обратил внимание, что в цикле чтения данных, который длится на один полутакт дольше, чем цикл чтения кода операции, реально данные все равно защелкиваются через тот же промежуток времени, что при чтении кода операции.

Т.е. этот лишний продленный полутакт чтения непонятно зачем. Возможно, для совместимости с 8080?

Тут нет разницы, в чем защелкиваются данные.

Я говорю о том, что не смотря на то, что длительность циклов обращения к внешней памяти для чтения опкода (1 такт) и данных (1.5 такта) - разная, внутренний цикл (внутри Z80) все равно остается одинаковым, и равен 1 такту. Поэтому увеличенный на 0.5 такта внешний цикл не играет никакой роли, все равно внутри процессора данные защелкиваются на 0.5 такта раньше, чем окончится внешний цикл.

Меня интересует, зачем это сделано? Я думаю, что до совместимости с предыдущей линейкой (i8080). Иного обьяснения у меня нет.

Эту тему просматривают: 2 (пользователей: 0 , гостей: 2)