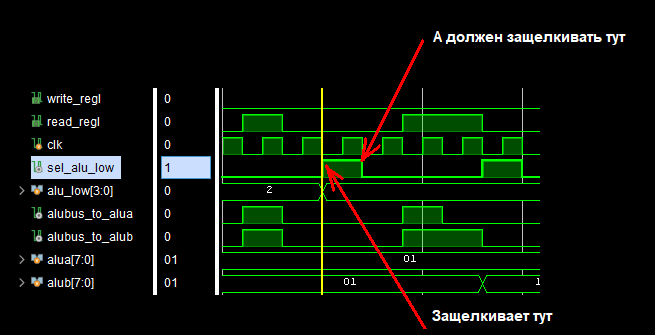

Дошел до модели АЛУ, и тут наткнулся на подозрение, что такая конструкция переводится в схему не так, как казалось бы должно:

Код:always @ (negedge clk) // RS-триггер выбора фазы работы АЛУ begin if (start_alu) sel_alu_low = 1; else if (req_alu_high) sel_alu_low = 0; endНо второй триггер почему-то защелкивает результат на 1 такт CLK раньше чем должен.Код:always @ (negedge clk) // Регистр фиксации младшего полубайта результата begin // if (sel_alu_low) // alu_low <= alu_out[7:4]; // end //

Совершенно непонятно, как это может быть.

Ответить с цитированием

Ответить с цитированием