В общих чертах все более-менее правильно описано было в

этой статье.

Так как подробные схемы и диаграммы в этой теме не пользуются популярностью, расскажу лишь кратко.

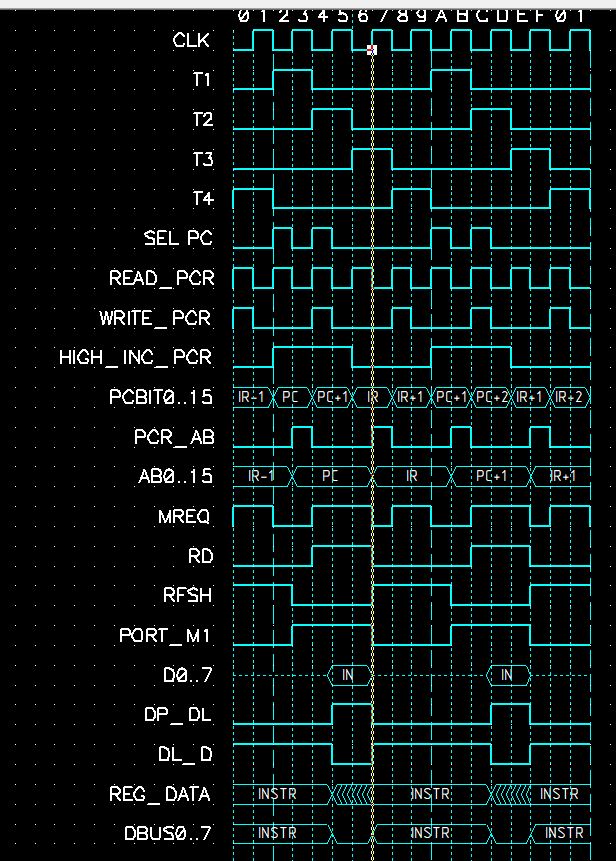

1. Вовсе не обязательно выдерживать длительность сигнала специального ресета такой, как описано в патенте. Импульс может быть длинной даже менее полутакта. Главное, чтобы во время фиксации ресета (в M1.T2.2) он был активен, а в M1.T2.4 уже не активен.

2. Импульс специального ресета устанавливается по М1.Т2, далее по M1.T1 следующего цикла происходит сброс регистра PC, а по M1.T2 импульс специального ресета снимается.

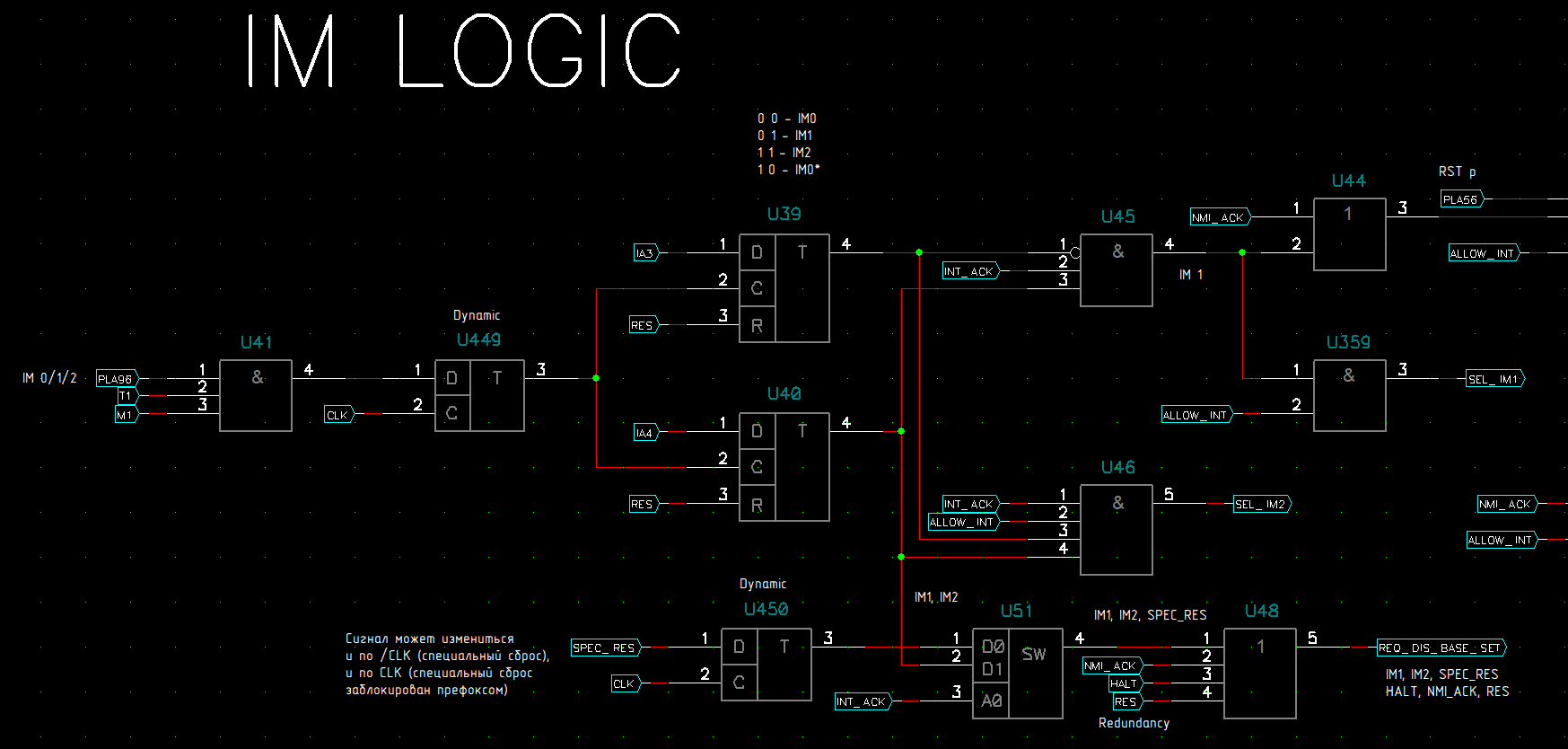

3. Импульс специального ресета задействует механизм запрета декодирования кода команды, который также используется в IM1,2, NMI, HALT. В этом режиме любая команда воспринимается декодером команд, как 00 (NOP).

4. Если специальный ресет поступил во время выполнения любой команды с префиксом, то выполнение специального ресета откладывается до окончания выполнения этой команды.

5. Также специальный ресет снимает режим HALT.

6. Если обычный ресет пришел во время M1.T2, то он задерживается на 1 такт.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию