Жестко только на первый взгляд. Надо просто почесать голову и придумать решение без асинхронных RS-триггеров. На самом деле, асинхронные RS-триггеры - зло. Почему?

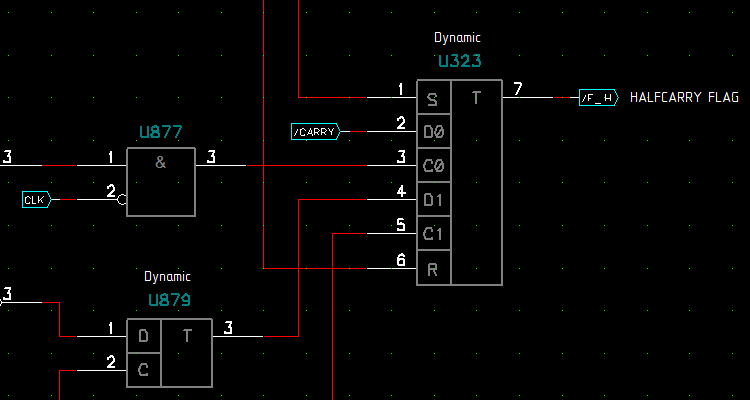

При переходе сигнала R (для S рассуждения аналогичны) из неактивного в активный уровень проблем не возникает. Триггер просто сбрасывается, независимо от входов CLK и D. Однако переход R из активного в неактивный уровень должен быть обязательно согласован с тактовой частотой. В противном случае может возникнуть метастабильность. Если снятие R и фронт CLK приходят на триггер почти одновременно - то неизвестно, какой (из-за задержек разводки связей на чипе и т.п. эффектов) придет раньше. И если вход D=1, то R может быть снят как раз в тот короткий промежуток времени, когда информация с входа D проходит на выход триггера. И тогда триггер может остаться в промежуточном состоянии между 0 и 1 на длительное время (один-два такта, изредка более). При этом, до перехода триггера в какое-нибудь (заранее неизвестное!) стабильное состояние, схема, которая смотрит на его выход, может увидеть несколько переключений.

Как лучше всего перевести схему с асинхронных на синхронные RS-триггеры - этот вопрос решается индивидуально в каждом конкретном случае. Если столкнешься с практическим примером, который трудно самому решить - приведи схему, попробуем покумекать вместе.

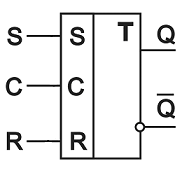

Это зависит от ГОСТов той страны, в которой ведется разработка. Иногда еще от "стандартов" фирмы-производителя FPGA. Конкретно у Xilinx приняты следующие обозначения:

триггер с асинхронным сбросом - FDC, вход сброса - CLR

триггер с синхронным сбросом - FDR, вход сброса - R

триггер с асинхронной установкой - FDP, вход установки - PRE (от слова Preset)

триггер с синхронной установкой - FDS, вход установки - S

По ГОСТ 2.743-91, триггеры обозначаются символами T или TT. Вход установки - SET или S, сброс - RES или R (синхронность или асинхронность задается не буквами, а графическим "указателем свойства выводов").

Что значит "многопортовыми"? Параллельные регистры с несколькими триггерами? Просто задаешь входные и выходные шины данных для этих регистров в виде "векторных" сигналов на языке (Verilog/VHDL). Задаешь один "процесс", запускающийся по фронту тактовой частоты. Внутри процесса (и, возможно, блока if) одна команда - запись выходных сигналов регистра на его выход. Еще можно сделать регистру вход разрешения записи (CE) путем помещения в "процесс" команды IF, которая позволяет запись на выходы регистра только если CE='1'. Триггеры внутри FPGA имеют вход разрешения записи, им можно и нужно пользоваться.

Для более подробной информации рекомендую документ Xilinx UG626 "Synthesis and Simulation Design Guide". Там глава 5 "Coding for FPGA Device Flow", подраздел "Registers in FPGA Design".

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию