Сообщение от

Titus

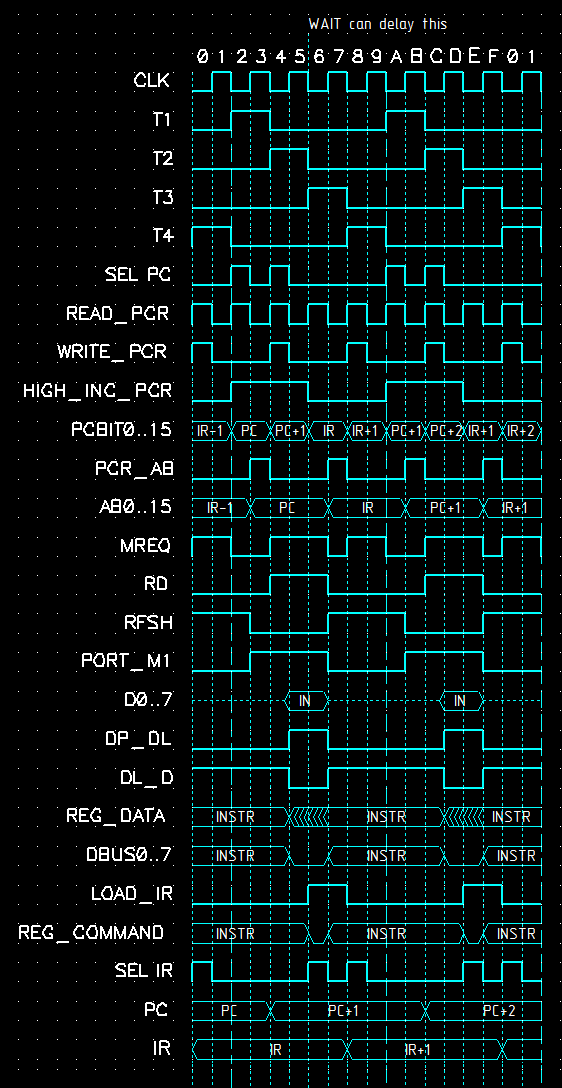

Если в ноере такта присутствует точка (T1.1 или T1.2), это означает, что имеется в виду 1-й или 2-й полутакт.

Номер полутакта может быть больше 2 вследствие прохождения сигналом промежуточных триггеров. Например, T1.3 обозначает третий полутакт от начала такта T1. Не смотря на то, что по времени он может совпадать с T2.1, правильнее обозначать его именно T1.3, т.к. он инициирован тактом T1.

В первом цикле любой команды в такте Т1.1 активны сигналы READ_PCR и SEL_PC, по которым регистр PC читается из регистрового файла и записывается в регистр PCR.

В такте T1.2 регистр PCR записывается в регистр адреса REG_ADR, содержимое которого выставляется на шину адреса AB0..15.

В этом же такте инкрементированное значение PCR записывается в регистр PCR2.

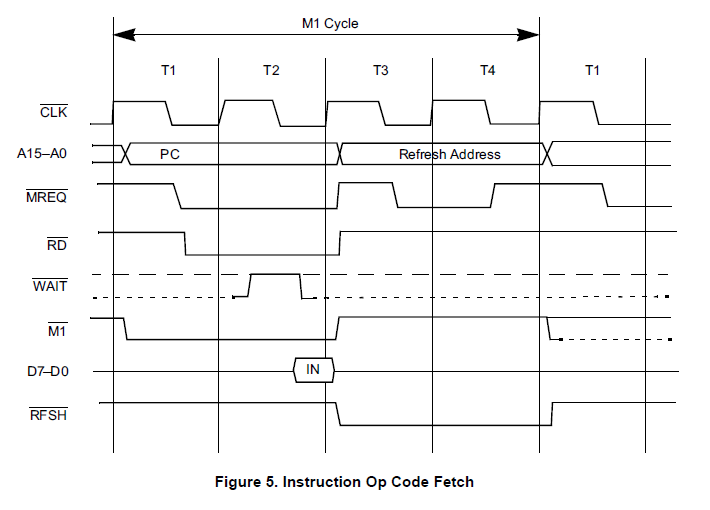

По переднему фронту такта T1.3 (T2.1) устанавливаются сигналы MREQ и RD, выдавая внешней схеме запрос чтения памяти.

Также в такте T1.3 (T2.1) происходит запись регистра PCR2 обратно в регистр PC.

По переднему фронту такта T2.2 устанавливается сигнал DP_DL, по которому данные с DB0..7 через шину DLATCH0..7 записываются в регистр REG_DATA.

По переднему фронту такта Т2.3 (Т3.1) устанавливается сигнал LOAD_IR, по которому данные с шины DBUS0.7 записываются в регистр команды REG_COMMAND. При этом в течение такта T2.3 (T3.1) на шине DBUS0..7 удерживается ноль.

Также в этом такте активны сигналы READ_PCR и SEL_IR, по которым регистр IR читается из регистрового файла и записывается в регистр PCR.

По переднему фронту такта Т3.2 снимается сигнал DP_DL, прекращая запись внешних данных в регистр REG_DATA.

В такте Т3.2 на шине DBUS0..7 появляется значение регистра REG_DATA и остается там до следующего такта T2.2.

Так же в этом такте данные с шины DBUS0..7 продолжают записываться в регистр REG_COMMAND.

Фактически фронт T3.2 - это момент защелкивания данных с шины DB0..7 в регистре REG_COMMAND.

Таким образом, с момента выставления сигнала RD и до момента защелкивания данных в REG_COMMAND отводится чуть менее 1.5 тактов.

В этом же такте регистр PCR записывается в регистр адреса REG_ADR, содержимое которого выставляется на шину адреса AB0..15.

В этом же такте инкрементированное значение PCR (инкрементируются младшие 7 бит) записывается в регистр PCR2.

В этом же такте сбрасывается сигнал MREQ.

По переднему фронту такта T3.3 (T4.1) сбрасывается сигнал LOAD_IR, прекращая запись регистра REG_DATA в REG_COMMAND.

В этом же такте происходит запись регистра PCR2 обратно в регистр IR.

В этом же такте устанавливается сигнал MREQ,

По переднему фронту такта T4.3 (T5.1) сбрасывается сигнал MREQ.

Таким образом, длительность цикла чтения - 1.5 такта (и более, если активен WAIT), длительность цикла регенерации памяти - 1 такт.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию