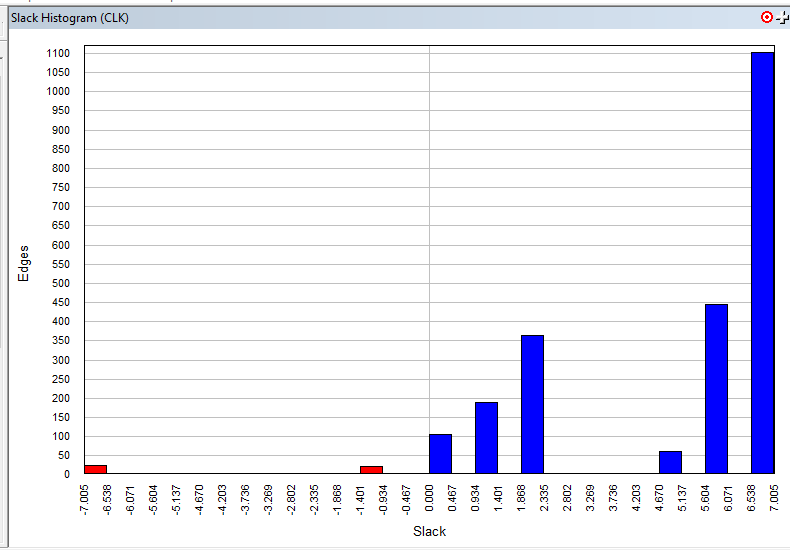

AlexG, всё верно. И именно поэтому надо смотреть в условный TimeQuest на Clock Skew или хотя-бы Fmax чтобы понимать, что фиттер положил насинтезированное так, что задержки укладываются в твой такт. Тогда проект будет работать на всех указанных тобой чипах в любых условиях, а не глючить в зависимости от фазы луны и желанию твоей левой пятки.

Побольше синих и отсутствие красных. И ещё, если попытаешься комбинаторику в такты зарулить без правильного преобразования оно тебе прокричит про ripple clock.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию