Сообщение от

Barmaley_m

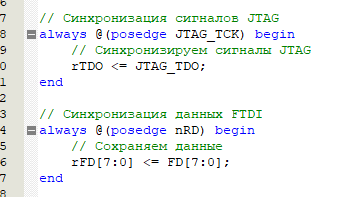

Однозначно второй вариант. По возможности надо делать так, чтобы все триггеры схемы тактировались одной частотой. Если какие-то части схемы работают на половине или других долях от этой частоты - то следует использовать вход триггеров Clock Enable (CE), описав его на HDL в виде команды if, наподобие твоего второго варианта, для достижения поставленной цели.

Деление тактовой частоты триггером и использование результата для тактирования какой-то части схемы имеет следующие недостатки:

1) Расходуются глобальные тактовые буферы (в примере Spartan6 - BUFG)

2) Поделенная тактовая частота будет из-за задержек элементов схемы и разводки выхода триггера на тактовый буфер и обратно сдвинута по фазе относительно исходной. Эти сдвиги затронут также все сигналы от триггеров, работающих от половины тактовой частоты. Все эти задержки будут отниматься от "бюджета времени" при переходе сигналов данных от триггеров, тактируемых полной тактовой частотой, на триггеры, тактируемые ее половиной, и обратно. В результате будет труднее обеспечить выполнение Timing constraints, снизится максимальная тактовая частота проекта.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию