Как бы да...

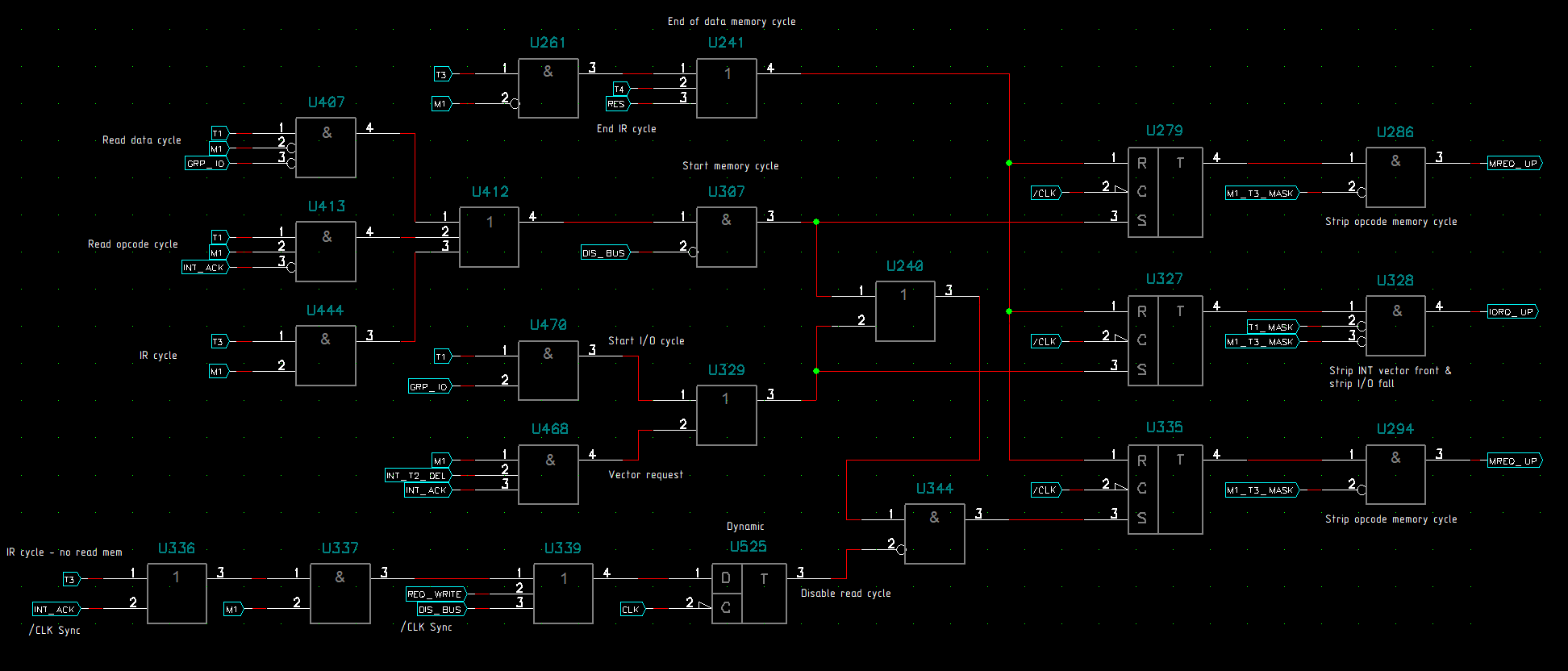

На самом низу - собственно реализация - получаем набор модулей, которые между собой соединяются между собой - получаем ТОП.

Там, где цыпляем между собой модули - логики лучше не рисовать.

ПС: раннее я предлагал поделить всю схему на блоки - обозвать их. и потом собирать из этих кубиков ТОП

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию