Фух!

Наконец-то перевел транзисторную схему Z80 NMOS в логическую, попутно причесывая и транзисторную.

Чем дальше понимаешь логику работы, тем лучше причесывается схема, группируется по функциональным блокам и т.д.

Логическая схема полу-причесана, поэтому это только первый этап.

Кстати, уже нашел всякие интересности. Например, странную избыточность в цепи выборки команд CB.

Наверняка, при анализе какие-нибудь тайны Z80 все-таки всплывут)

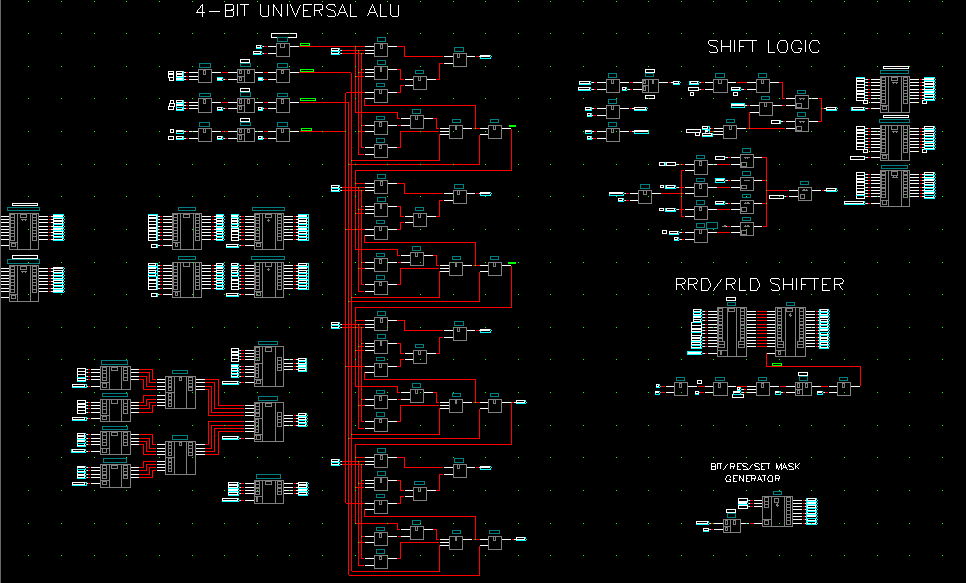

Для затравочки кусочек с ALU:

- - - Добавлено - - -

Из интересностей:

Всего в процессоре 14 16-битных регистров. 12 регистров (IX, IY, HL, DE, BC, HL', DE', BC', AF, AF', WZ) сидят на основной шине, а два регистра PC и IR расположены на отдельной шине, причем при необходимости между этими двумя шинами может выстраиваться мост, чтобы получался доступ к PC и IR с основной шины.

Впрочем, оно и понятно, т.к. PC и IR имеют свои блоки инкремента/декремента, сравнения и т.д., т.к. используются параллельно с основным вычислительным блоком.

- - - Добавлено - - -

И похоже, что всякие блок-схемы Z80, в фирменно документации и не только - не имеют никакого отношения к реальной структуре процессора. Может просто я не все их видел.

Ответить с цитированием

Ответить с цитированием