SPI -- это в первую очередь память. Либо локальная флешка в SOIC8, либо SD карта, либо и то и другое. Ну а далее, разумеется, идут и часики, и ЦАП/АЦП, и дисплеи, и клавиатуры, и расширители ввода-вывода, да в принципе, там и байтбластер замутить можно.

Кстати! Насчёт байтбластера -- это идея!

- - - Добавлено - - -

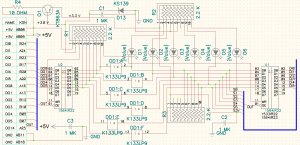

Гребёнка необходима. Все 4 сигнала SPI, дополнительные CS, 5В, очень желательно -- 3,3В. SD карты хотят их. Правда, Грифон уже нечто подбное соорудил ...

- - - Добавлено - - -

Сообщение от

MM

Поэксперементировал - да, при 4-бит ( QUAD SPI ) режиме чтения 2 Кбайт есть, может немного больше.

Хм. Влобовая реализация 1-бит байтового обмена с развёрнутым кодом даёт 3+ кбайт/сек на чтение. Код:

Код:

; SPI bit-banging, read

; r0 -- bit shift buffer

; r1 -- destination memory pointer

; r2 -- 77777

; r3 -- SCLK->0 + SDO->1

; r4 -- 177714

; r5 -- SCLK->1 + SDO->1

; 177714.15 -- SDI

; @sp -- byte count

1$: ; 7

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 6

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 5

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 4

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 3

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 2

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 1

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; 0

mov r3, @r4

cmp r0, @r4

mov r5, @r4

rolb r0

; store

movb r0, (r1)+

dec @sp

bne 1$

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию