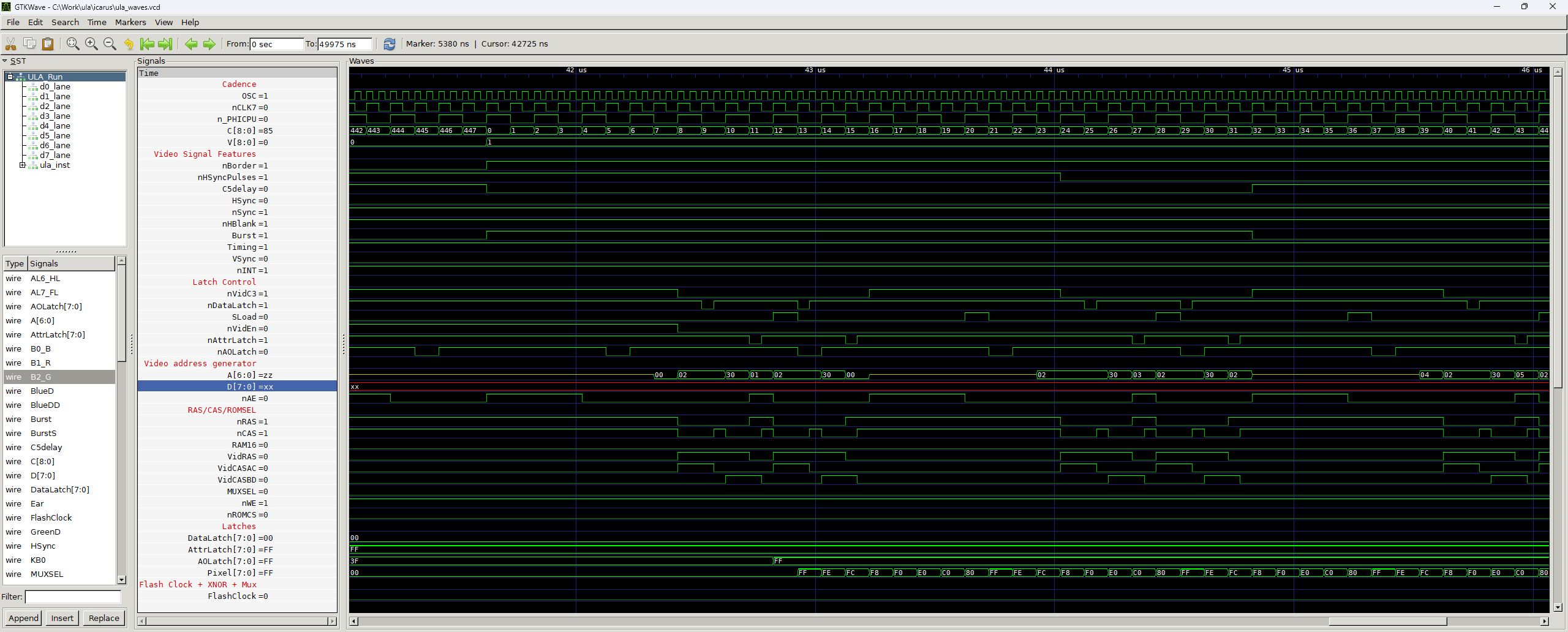

Бутанул юлу в икарусе, можно спокойно ковырять и ставить эксперименты:

Для этого пришлось сделать все норы - бехавиорал, чтобы симулировать RS флип флопы, на которых построены элементы памяти.

module ula_nor ( a, b, x);

input wire a;

input wire b;

output reg x;

// To simulate RS flip flops we use behavioral model

always @ (a or b) begin

if (a == 1'b0 && b == 1'b0) begin

x = 1'b1;

end

else

x = 1'b0;

end

// nor (x, a, b);

endmodule // ula_nor

Тестбенч тут: https://github.com/emu-russia/ula/tree/main/icarus

Ответить с цитированием

Ответить с цитированием