Битва за Личитанг.

Еще весной были прикуплены недорогие и достаточно любопытные платки "Lichee Tang Risc V Development board" от Sipeed.

Вот такие.

Там установлена китайская FPGA от Anlogic EG4S20, достаточно толстая, уровня Cyclone EP3C16/EP3C25, с бОльшим объемом

статической памяти и, главное, 32-битной SDRAM на 8MB, упакованной в тот же корпус, с обещанием работать на 200МГц.

Была скачана IDE для нее - Династия Танг, первое впечатление оказалось очень даже ничего, и было решено портануть

процессоры 1801 на эту платформу.

Скрытый текст

[свернуть]

Создал проект и сразу уперся в различия PLL, было долго непонятно как генерировать нужное. Входная частота кварца на плате

в 24МГц отличается от остальных FPGA-шных отладочных плат 50МГц и стандартный ряд частот проекта - 50/66/75/100 МГц оказалось

поддержать непросто. Оно умеет делить выходную частоту на коэффициент и потом сравнивать со входной, тоже деленной на

заданный коэффициент, то есть - если надо 50МГц то надо поделить на 25 и получить 2МГц, и входные 24МГц поделить на 12 и получить

опорные 2МГц. Но - фазовый детектор в EG4S20 начинает работать от 10МГц! Пришлось создавать фантомный выход, который

никак не используется, только для обратной связи, задать VCO 600МГц как 24МГц * 25 и потом уже 600 делить на нужные

6/8/9/12 для получения требуемого ряда.

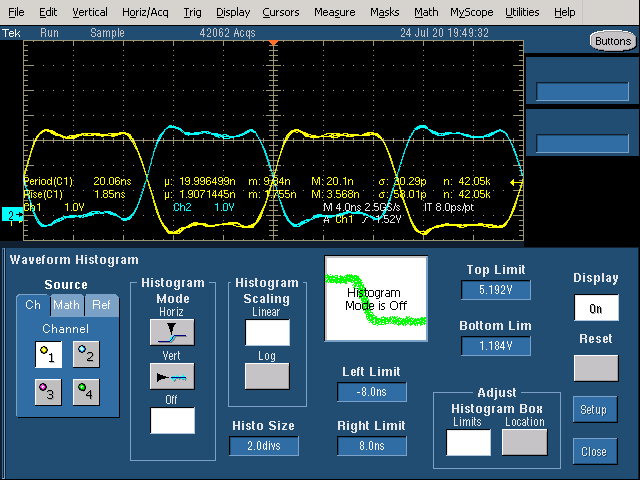

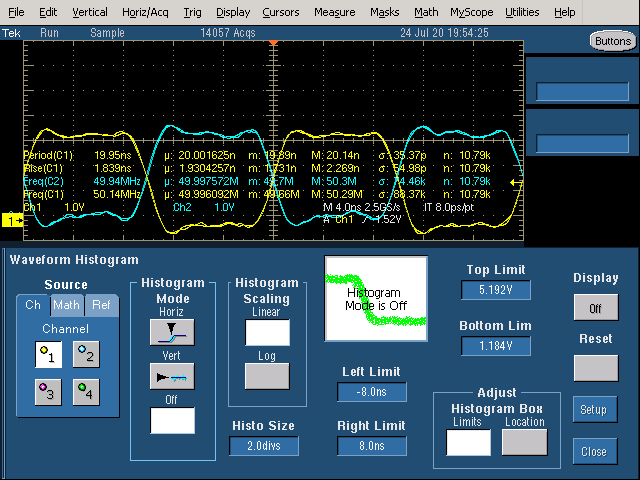

И верифицировать результат осциллографом, потому что сгенерированные IP показывали в исходниках странноватое.

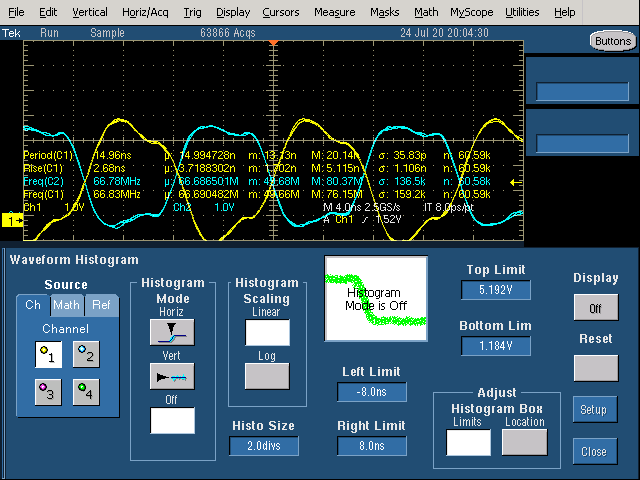

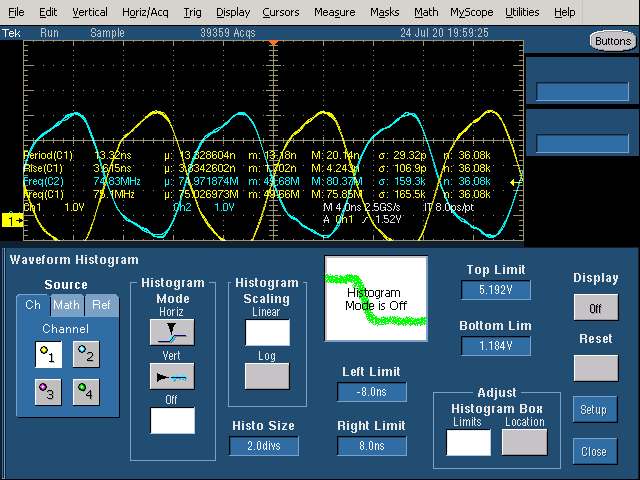

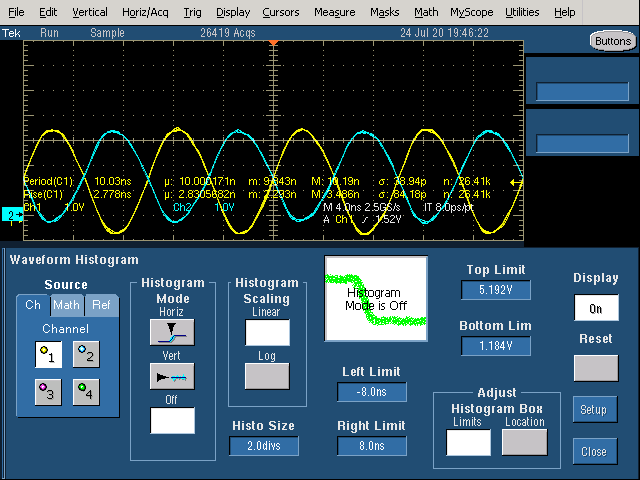

В итоге PLL получилось победить, результаты (png, траффика нет):

Кстати, видно как меняется форма сигнала с ростом частоты - это именно перестает тянуть выход микросхемы (пассивные щупы/скоп с полосой 500МГц).

Идем дальше и нарываемся на ошибки компиляции - оно не видело определений из глобального `include "config.v"

Я уже даже решил что кетайци такое не осилили, но - нет, дело оказалось в своеобразной трактовке управляющие коментариев (синтез/симуляция)

Код:

// synopsys translate_off

`include "config.v"

// synopsys translate_on

Ну и потом оно как-то очень быстро пошло - сгенерировал IP для памяти, влючая специальный случай двухпортовой для регистрового файла 1801ВМ1,

и 1801ВМ1/ВМ2 быстренько заработало. Но вот на LSI-11 - засада, оно не распознало infer ROM, как оно уже задрало - у каждого вендора свои заморочки

со встроеннйо памятью, нужно индивидуально шаблон подгонять.

В-общем, на github выложено обновление:

- добавлена плата QMTech на Cyclone-V

- добавлена плата QMTech на Cyclone-10LP

- добавлена плата Lichee Tang Risc V на Eagle EG4S20 - LSI-11 не работает

Добиваю LSI-11 и буду думать о встроенной SDRAM. Впечатления от среды "Tang Dynasty" нормальные, компилирует быстро, шьет нормально

(программатор встроен в плату), не падает, есть Verilog линтер на каждое сохранение. Но редактор убоговат, настроек немного, но если там

заниматься только портирование а не собственно разработкой - то все просто отлично. Сама EG4S20 для ретропроектов просто отлично ложится.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию

Легли или нет, будет с одной стороны понятно первого августа (обязательное условие 1), а потом - ближе к концу августа (тут сказать сложней, когда, обязательное условие 2)

Легли или нет, будет с одной стороны понятно первого августа (обязательное условие 1), а потом - ближе к концу августа (тут сказать сложней, когда, обязательное условие 2)