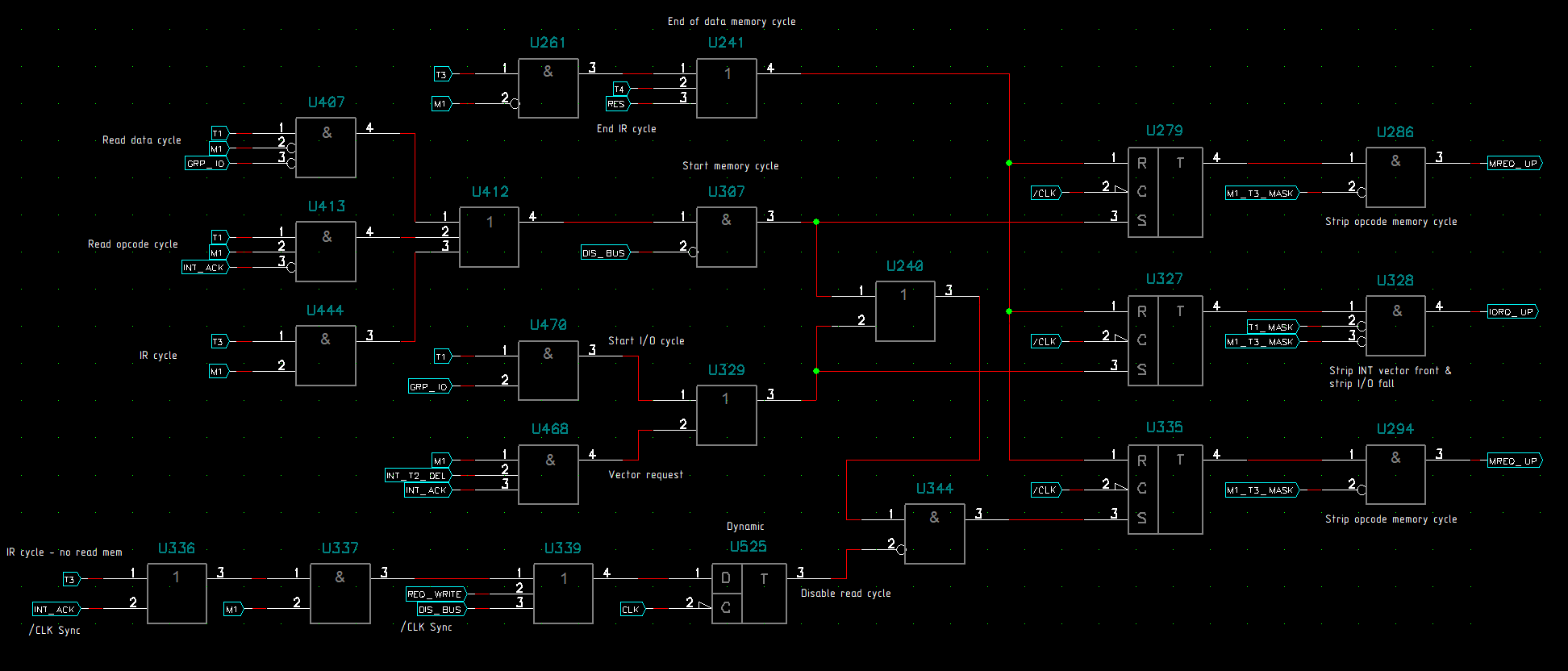

Переделал блок управления памятью в полностью синхронный вариант.

Пришлось пол-дня повозиться, крепкий орешек.

Все дело в том, что это самый кривосинхронный блок в процессоре. Одни циклы длятся 2, другие 3, третьи 4 ПОЛУ-такта, не такта. Да и еще в зависимости от разных условий. Самым оптимальным оказалось добавить на выходные линии простые обрезалки сигналов в нужные фазы. Тут пол-такта отрезаем, сям пол-такта. Тут режем, тут не режем, а тутрыбу заворачивали. Зато вынеся нестандартности за скобки, внутри схемы остался качественный синхронный дизайн.

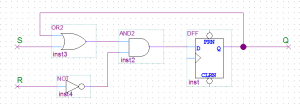

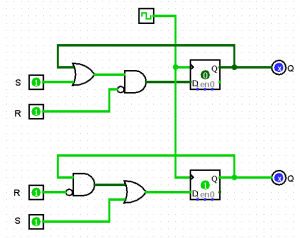

Изначально попробовал - как Vivado отнесется к RS-триггерам, у которых что-то устанавливается по спаду CLK, что-то по фронту? Оказалось, что никак вообще. И это к лучшему.

Скрытый текст

[свернуть]

- - - Добавлено - - -

Да, кроме того, в оригинальной схеме каждый из трех триггеров мог встать 'р@ком', если в неподходящие T-циклы приходил ресет. Особенно короткий ресет. Но повторять это нет смысла, потому что все равно плавающее кратковременное состояние не повторишь, а при ресете длинной >1 такта и так все нормализуется. Даже в оптимизированной текущей схеме еще не убран кофликт R и S при неподходящем времени ресета.

- - - Добавлено - - -

Интересно, как себя ведет Xilinx, если на R и S поданы 1?

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию