5 лет назад (нифига себе время летит), в теме Цифровая археология: 1801 и все-все-все с легкой руки нашего замечательного специалиста Vslav'a, я начал заниматься реверсом 1515ХМ2-001 (Обновленная версия КА1515ХМ1-031, с исправленными ошибками). В ней находится звук, таймер, контроллер клавиатуры от всеми нами любимой УКНЦ. Отреверсив около 25% чипа, я забросил это дело на неопределенный срок, и подняв недавно материалы, обнаружил, что многое подзабылось, а заметки, сделанные по данному проекту, слишком лаконичны, чтобы легко вьехать в тему снова. Поэтому прежде всего я решил формализировать то, что наработал тогда, и перевести заметки в легко понимаемый вид.

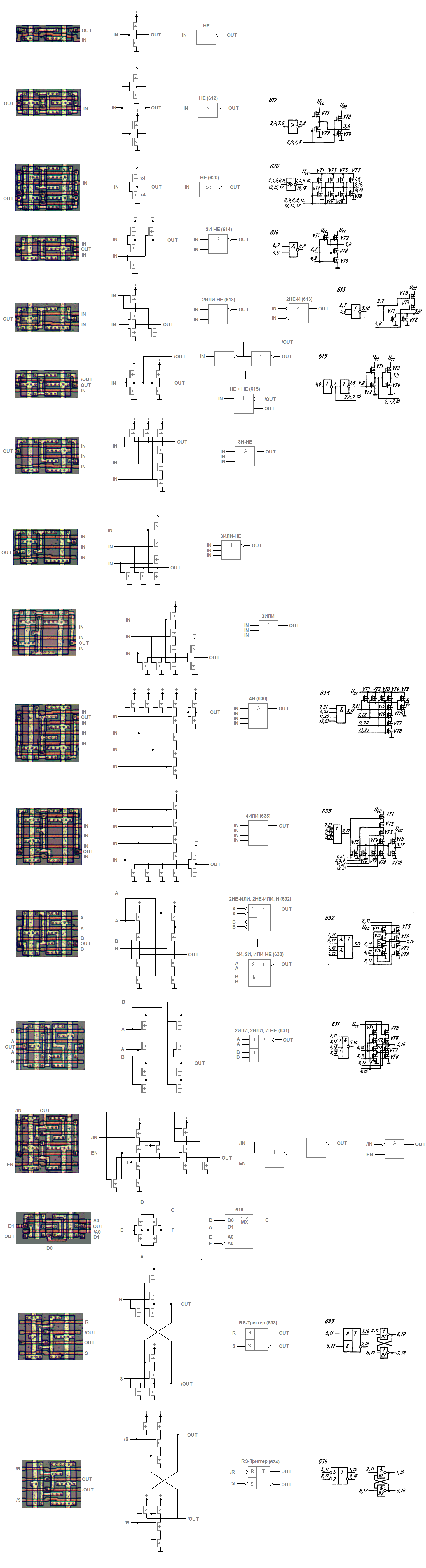

Библиотека элементов

Простая логика

[свернуть]

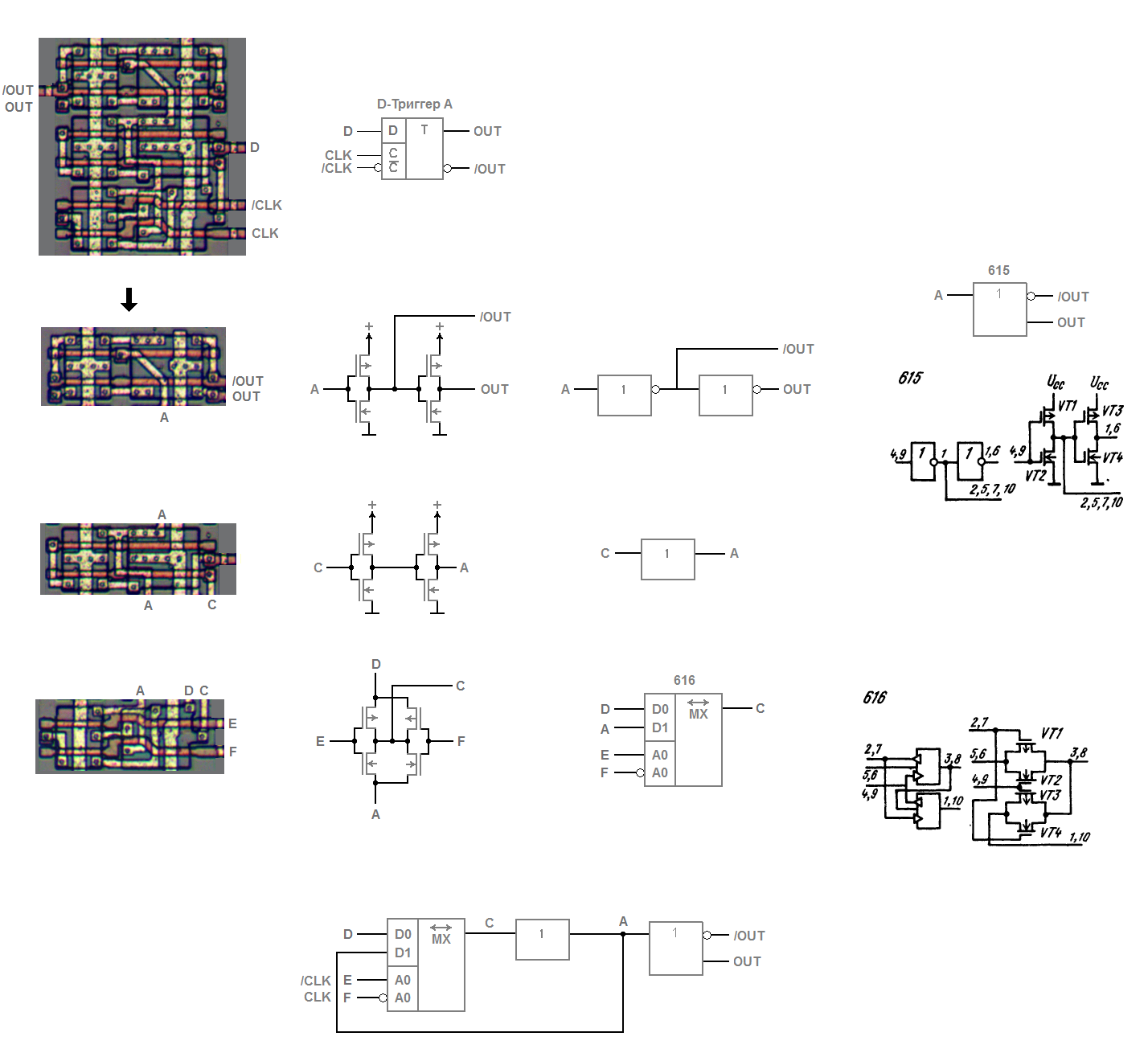

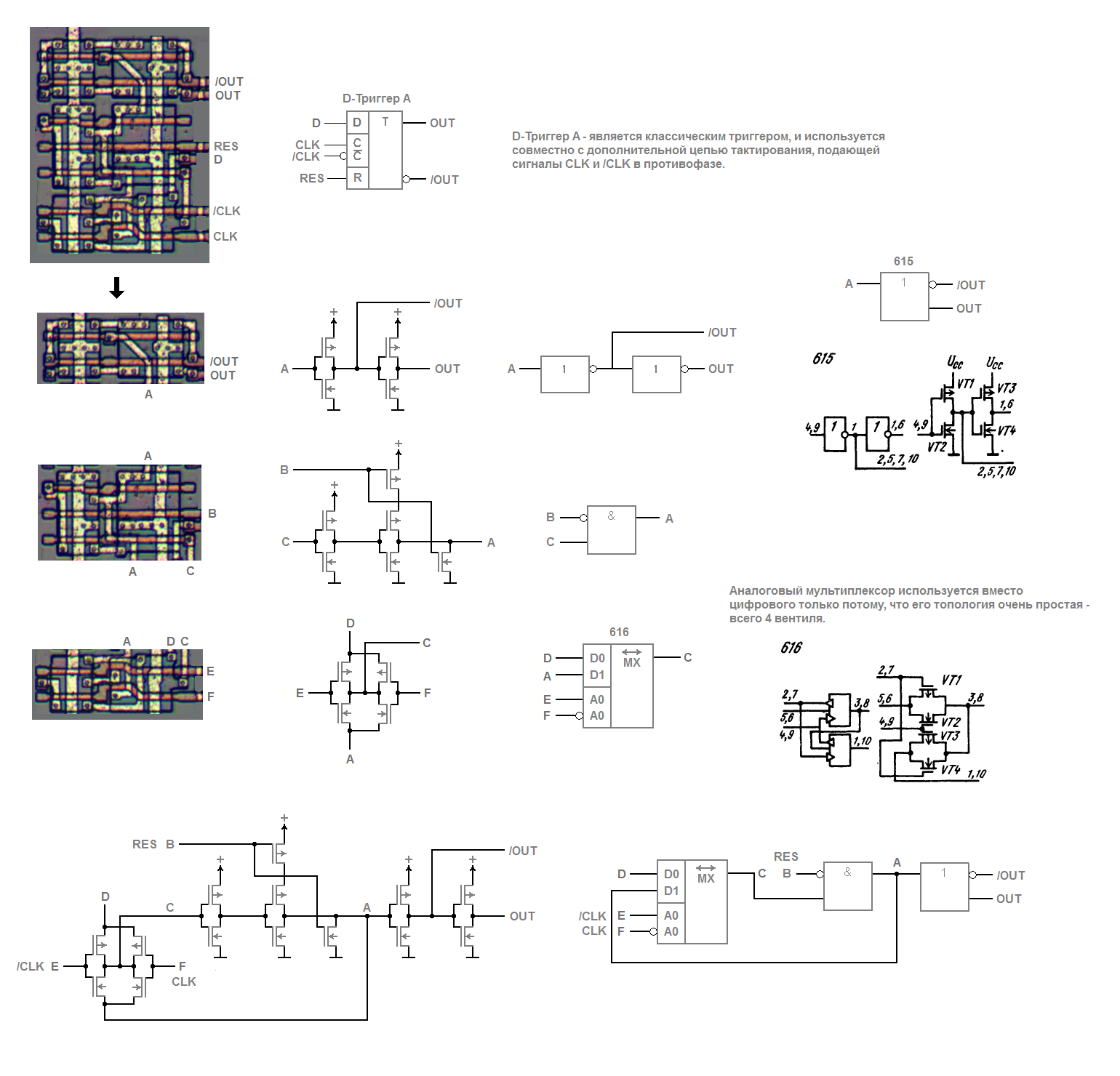

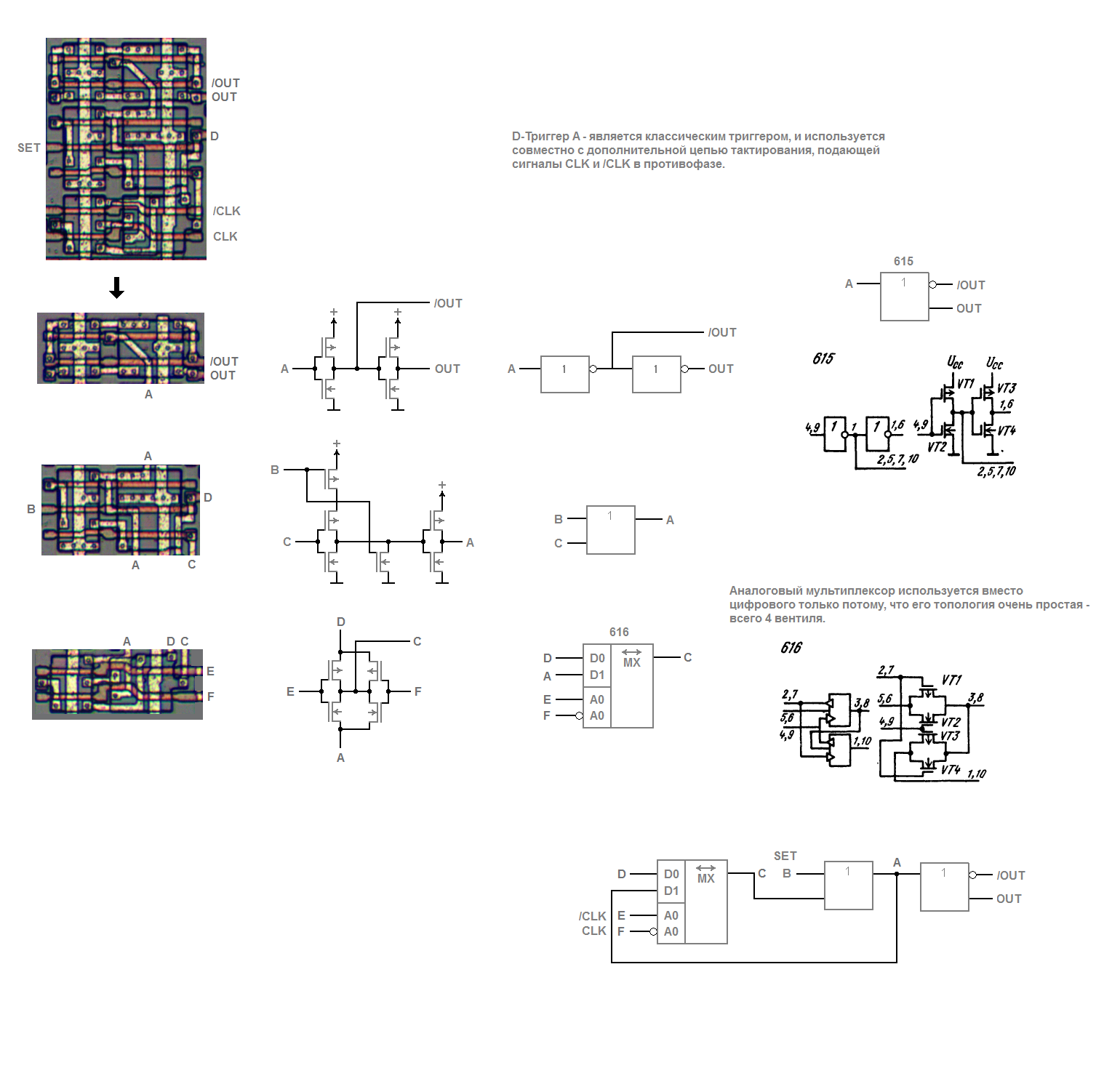

Триггеры:

D-Триггер, тактируемый единицей

[свернуть]D-Триггер-R, тактируемый единицей

[свернуть]D-Триггер-S, тактируемый единицей

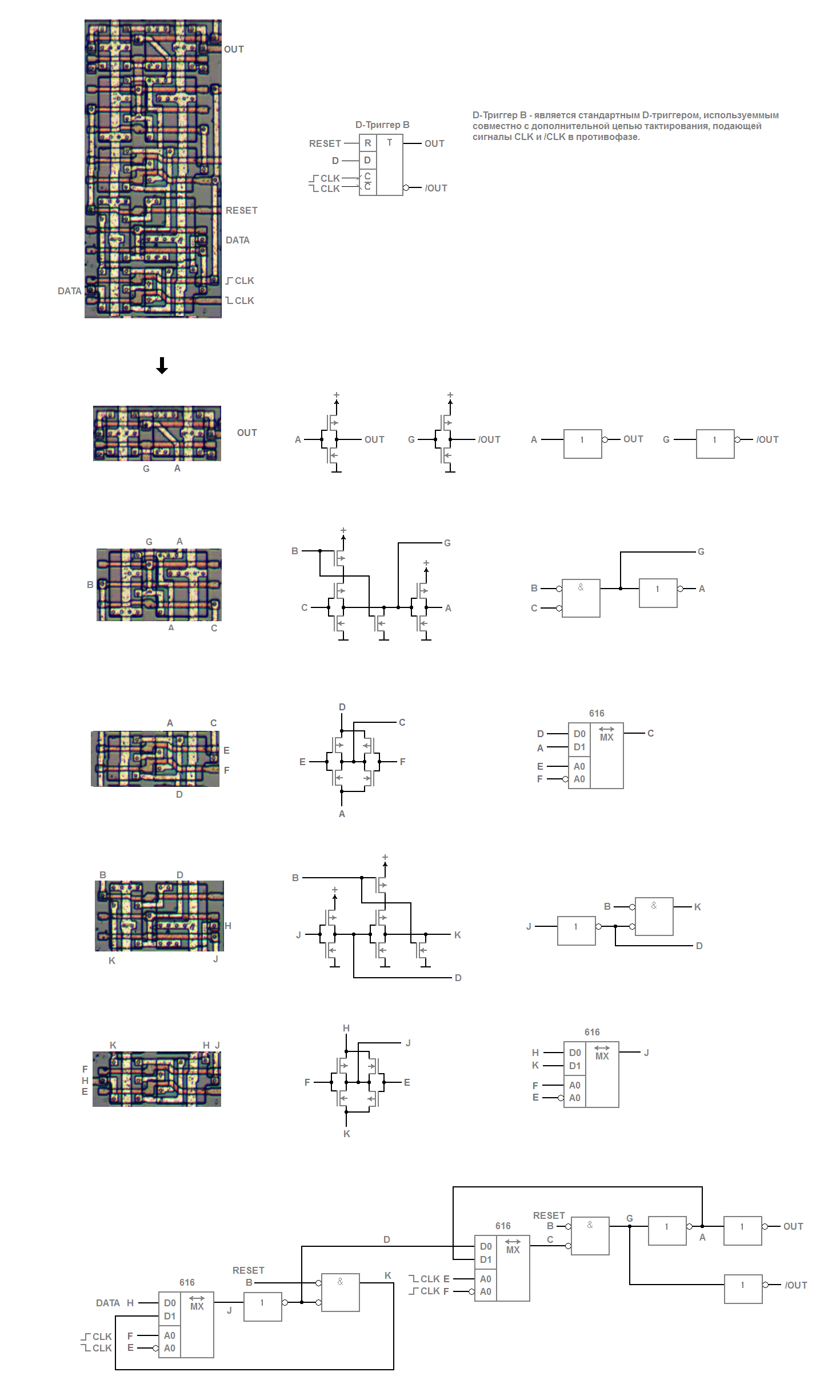

[свернуть]D-Триггер-R, тактируемый фронтом

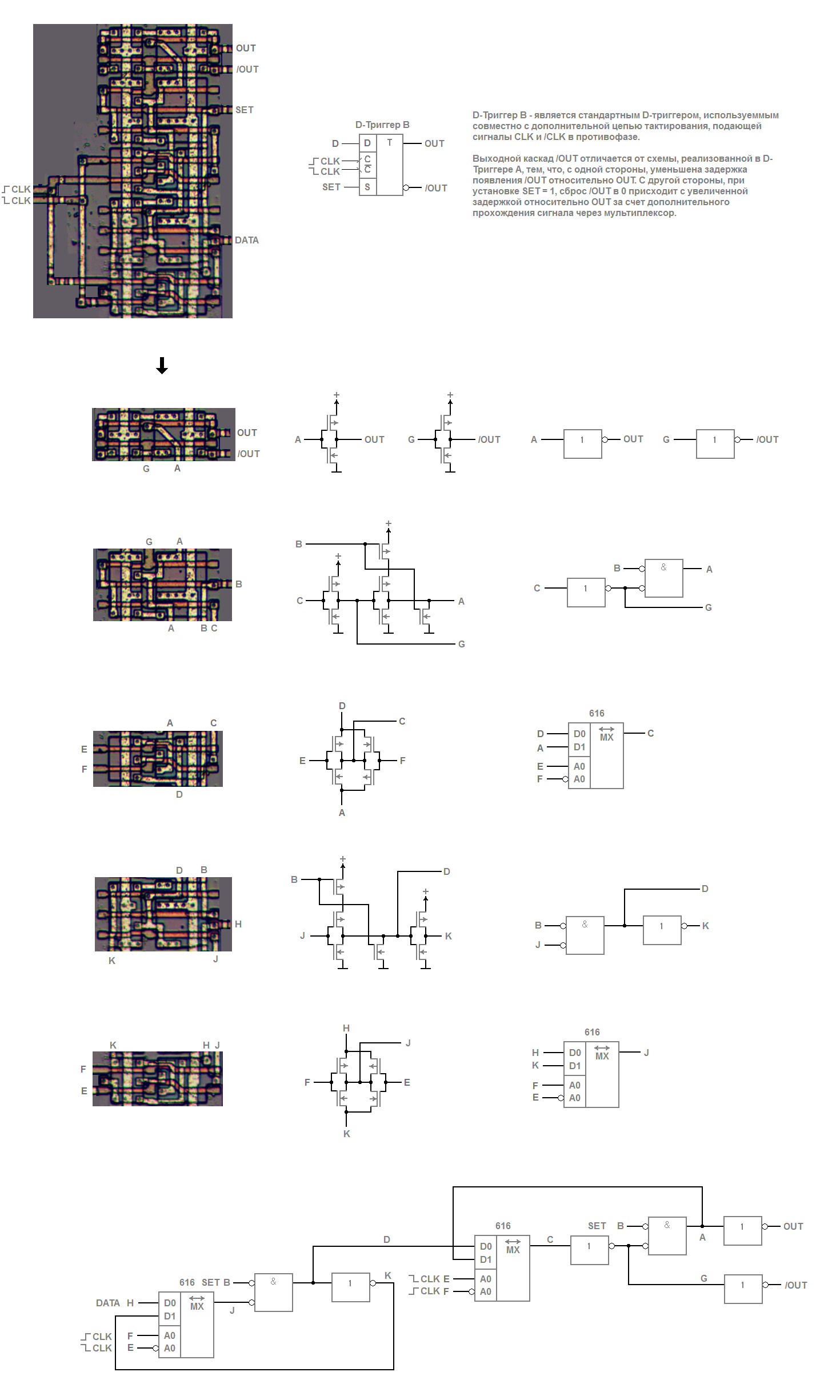

[свернуть]D-Триггер-S, тактируемый фронтом

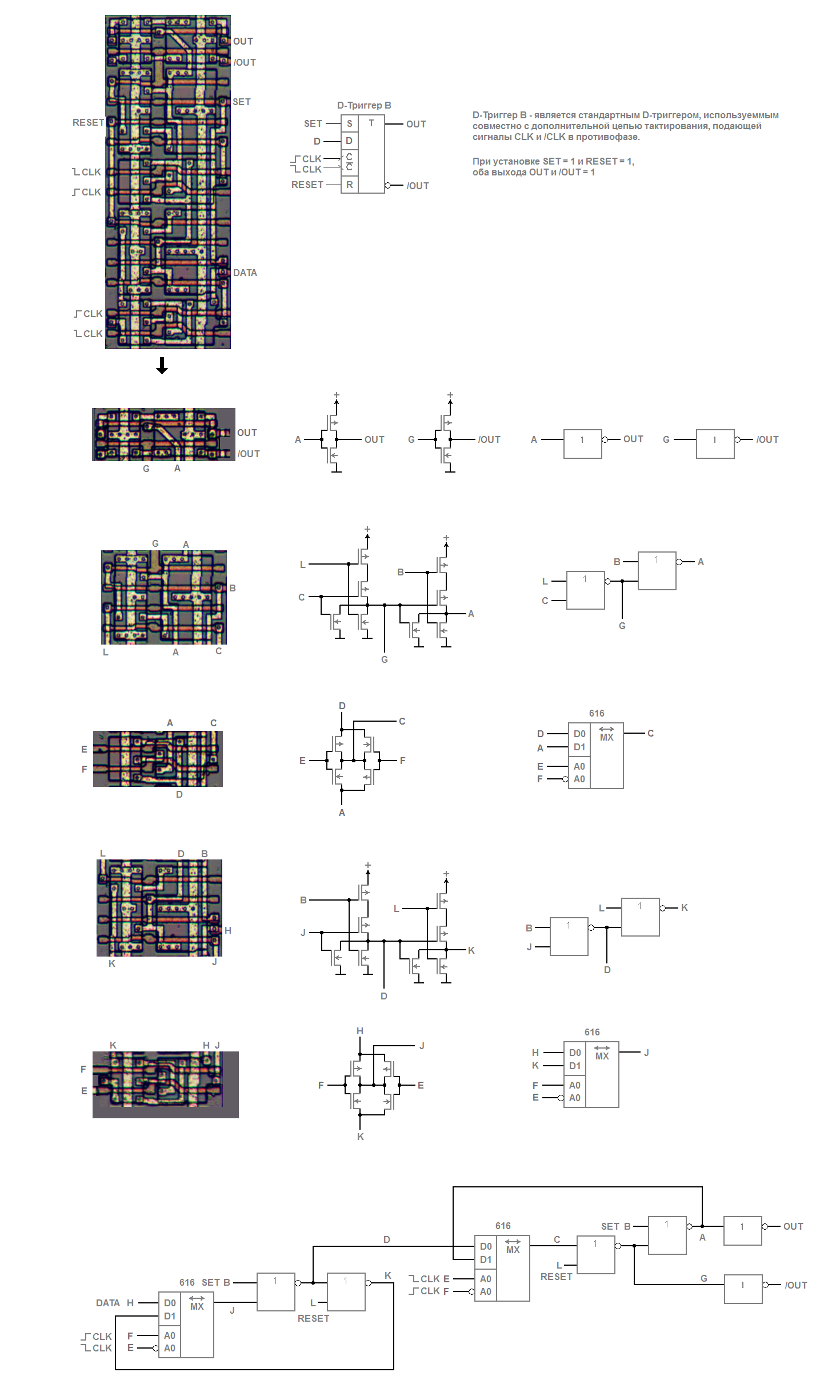

[свернуть]D-Триггер-RS, тактируемый фронтом

[свернуть]

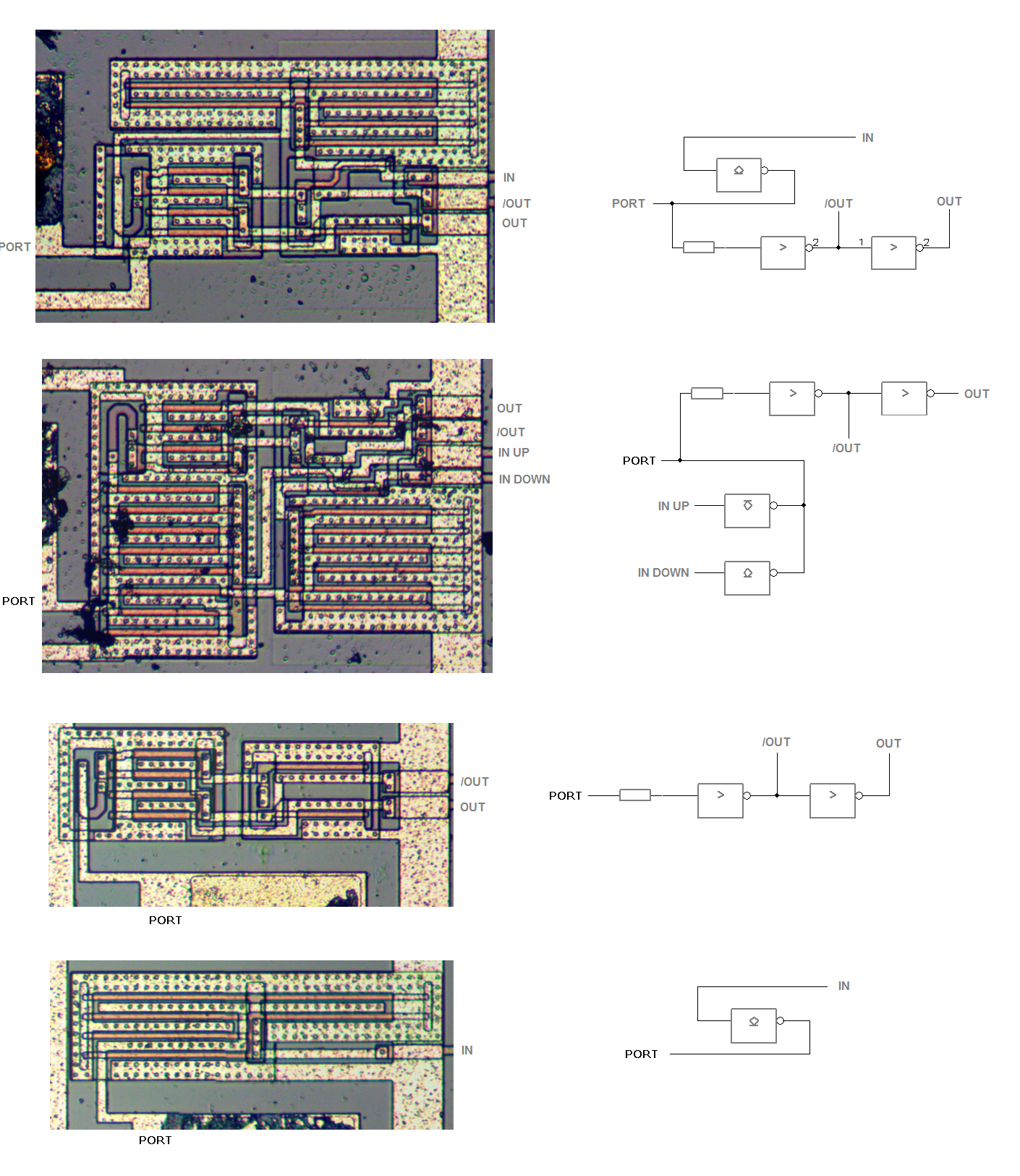

Порты ввода-вывода

[свернуть]

[свернуть]

Архив с оригинальным и оптимизированным реверсом 1515ХМ1,2 для P-CAD качать здесь.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию