Сообщение от

Vslav

В тестовой SoC есть прерывания от таймера, я проверю восстановление PSW8 и адрес wb_adr_o[16].

Да тут аппаратные прерывания как таковые для проверки не нужны.

Тут такая ситуация. Монитор по команде Т переписывает весь тестовый код из ПЗУ в младший банк ОЗУ и передает туда управление командой START. Далее отрабатывается тест, и затем происходит возврат в монитор вот таким способом:

Код:

ROM:002306 loc_2306: ; CODE XREF: sub_1570+104↑J

ROM:002306 ; default_int_handler+20↑J ...

ROM:002306 012746 000740 mov #740, -(SP)

ROM:002312 012746 170004 mov #loc_170004, -(SP)

ROM:002316 000002 rti

По адресу 170004, а это теневой банк ОЗУ, лежит команда JMP на бесконечный цикл обработки пультовых команд. И вот в этот момент, после RTI, и происходит незапланированное прерывание. Понятно, что если сигнал SEL не поднимется, то так и будет - после RTI управление уйдет на несуществующие адреса.

Надо это дело проверить. Я написал простенькую тестовую программку:

Код:

.WORD START

.WORD 0

.= 100

START:

MOV #410,SP

MOV #740,-(SP)

MOV #RMON,-(SP)

RTI

RMON:

MOV #MSG2,R3

CALL printstr

MFPS R3

CALL PNUM

STOP:

BR STOP

MSG2: .ASCIZ <15><12>"* PSW = "

Эта программка моделирует вышеописанный возврат в монитор - заталкивает в стек PSW с поднятым 8 битом. Запускаю. В терминале:Вроде все правильно, бит 8 PSW установился.

Дальше чисто программными способами, без изменения схемы, не проверить. У меня на моей плате есть 4 светодиода. Я подвесил на один из них бит 16 адреса:

Код:

reg [16:0] indaddr;

always @ (posedge wb_stb) indaddr [16:0] <= wb_adr [16:0];

assign led0=indaddr[16];

Запускаю схему - светодиод не светится. То есть adr[16]==0. А поскольку программа в конце зацикливается и начинает топтаться по одним и тем же адресам, то все транзакции на шине должны быть с wb_adr[16]==1, и светодиод должен ярко светиться.

Вот она, проблема.

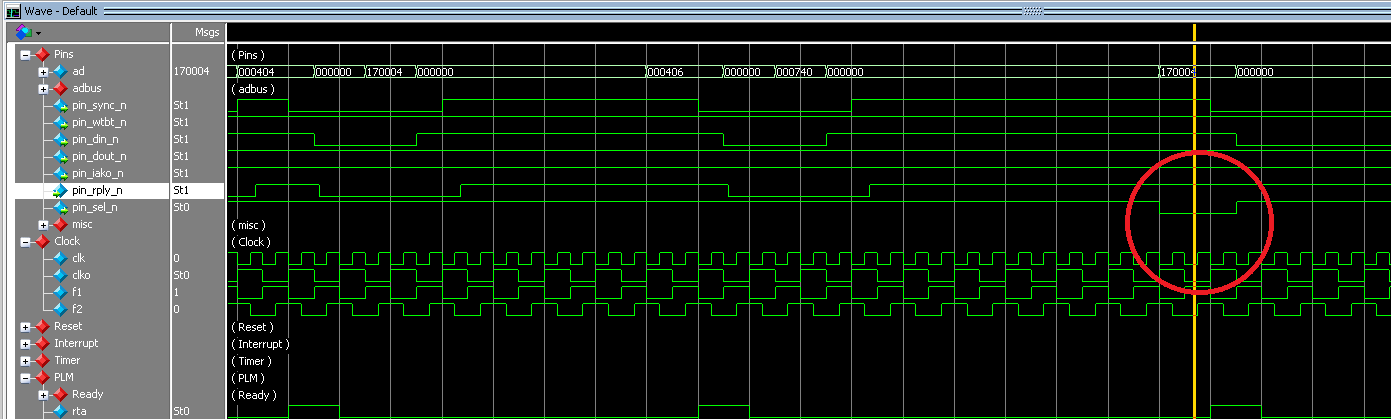

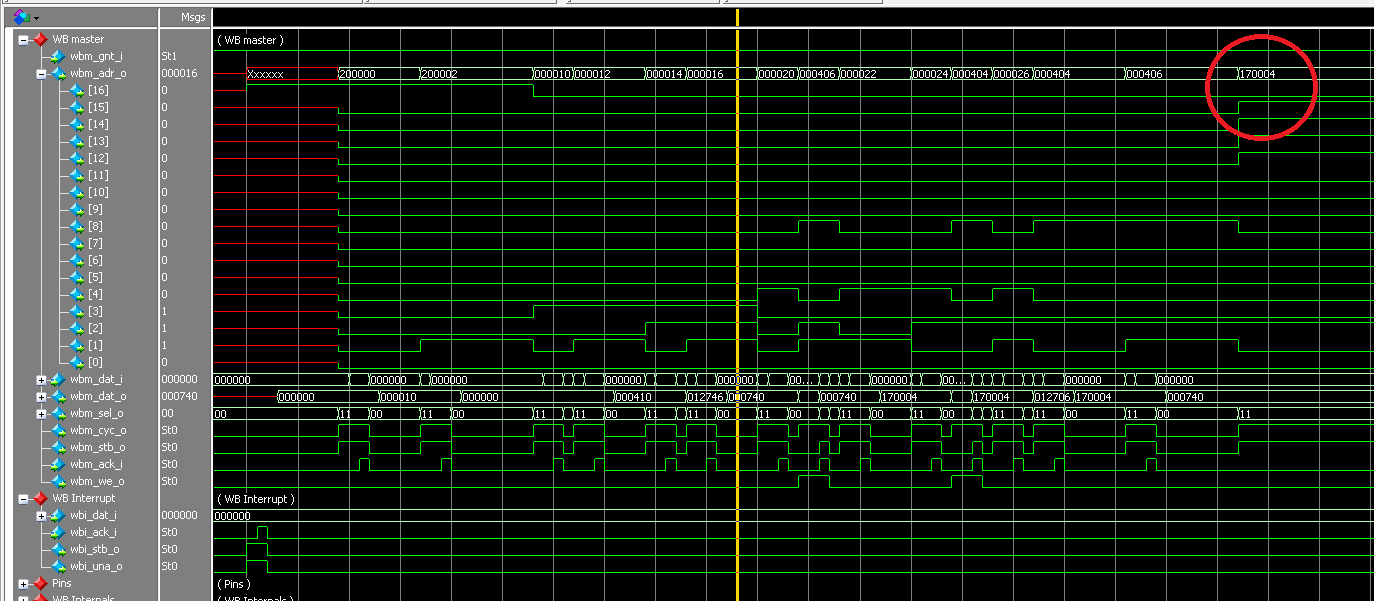

Остается промоделировать все это в моделсиме. Осциллограмму сюда я вставлять не буду, бесполезно это, прикладываю ее в архив. На ней хорошо видно:

1. Процессор читает слово 740 с адреса 000406. Это он из стека достал новый PSW.

2. По адресу 000116 читается 12703. Это уже выбирается первая команда после возврата по RTI. Адрес - именно 000116, ,бит 16==0, то есть перехода в режим пульта не было. Хотя в PSW бит 8 поднялся.

Вот и все мои на данный момент изыскания. Прикладываю архив с тестовой программкой. Конечно, запускать ее имеет больше смысла в симуляторе.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию