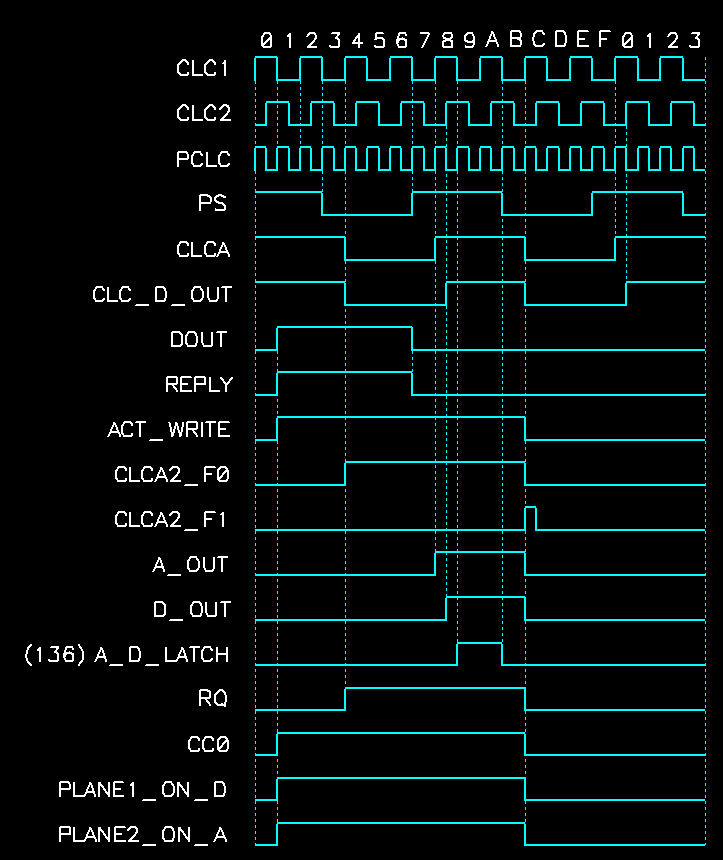

Набросал растактовку записи в регистр планов 1&2 для ХМ1-032.

Все нарисовано и описано чисто теоретически, глядя на отреверсенную схему, без моделирования.

Описание:

Наименоваия сигналов:

CLC1 - тактовый сигнал 6.25МГц (F1), он же тактовый сигнал CLCI для PPU (ПП)

CLC2 - тактовый сигнал 6.25МГц (F2), повторяет CLC1 со смещением на 1/4 такта.

PCLC - тактовый сигнал 12.5МГц (Pixel clock), получаемый из CLC1 и CLC2 внутри большинства чипов. Также является тактовым сигналом видеоконтроллера (ХМ1-136). Один такт PCLC соответствует одной точке экрана в разрешении 640. В дальнейшем тактовым сигналом будет называться именно PCLC.

PS - сигнал арбитра доступа к памяти PPU. Генерируется видеоконтроллером (сигнал PSG). Низкий уровень устанавливается во время точек 1, 2, 3, 4. В этой фазе шиной ВОЗУ владеет PPU. Высокий уровень устанавливается во время точек 5, 6, 7, 0. В этой фазе шина ВОЗУ свободна, и может использоваться для передачи данных между ХМ1-032 и ХМ1-136. Наружу сигнал выводится в инверсном виде (/PSG).

CLCA - сигнал арбитра PS со смещением на 1 такт. Каждый цикл начинается с низкого уровня.

ACT_WRITE - устанавливается по фронту записи в регистр планов. Сбрасывает по CLCA2_F1 (фаза завершения).

CLCA2_F0 - фаза F0. Запись данных на шины D0..D7 и A0..A7. Активна весь цикл CLCA.

CLCA2_F1 - фаза F1. Завершение. Активируется по завершению цикла CLCA.

RQ - сигнал запроса обмена с видеоконтроллером. Повторяет CLCA2_F0. Наружу выведен в инверсном виде (/RQ).

CC0 - сигнал запроса записи в планы 1 и 2. Повторяет ACT_WRITE. Наружу выведен в инверсном виде (/CC0).

Описание работы:

Запись в регистр планов 1&2 (PLANE12, адрес 177014) начинается по переднему фронту DOUT. Одновременно с этим устанавливается сигнал подтверждения записи RPLY. Таким образом, запись в регистр планов имеет для процессора нулевую задержку. Одновременно с этим устанавливается сигнал CC0. Также во время активного DOUT данные с шины AD защелкиваются в регистре PLANE1_DATA (младший байт), и регистре PLANE2_DATA (старший байт). Если происходит байтовая запись (активен WTBT), то при записи по четному адресу, блокируется запись в регистр PLANE2_DATA, а при записи по нечетному адресу блокируется запись в регистр PLANE1_DATA. Это означает, что в случае байтовой записи, незадействованная часть регистра планов сохраняет свое предыдущее значение.

По отрицательному фронту CLCA (такт 4) устанавливается сигнал RQ.

По положительному фронту CLCA (такт 8) на шину A0..A7 выводится содержимое регистра PLANE2_DATA.

Через пол-такта (такт 8.5) на шину D0..D7 выводится содержимое регистра PLANE1_DATA. Задержка вывода на пол-такта, очевидно, снижает шум на шинах.

Еще через пол-такта по внутреннему сигналу видеоконтроллера A_D_LATCH (такты 9 и 10), содержимое шин A0..A7 и D0..D7 защелкивается видеоконтроллером с шин AG0..AG7 и DG0..DG7 в регистрах DC_H, и DC_L, соответственно.

И еще через один такт (такт 12) процесс завершается.

Шины A0..A7, D0..D7 освобождаются, сигналы RQ, CC0 переводятся в неактивное состояние.

- - - Добавлено - - -

Как видно из растактовки, циклы несколько отличаются от того, что описано в журнале ПК УКНЦ 1'95.

Ответить с цитированием

Ответить с цитированием