Попробовал нарисовать теоретические графики цикла чтения.

Ох, и сложное это занятие по сравнению с 1515ХМ.

Разумеется, моделировать на симуляторе и проверять в миллион раз практичнее и безошибочнее.

Зато в теории можно нарыть какие-то баги, нюансы и т.д. А уже потом их можно моделировать, чтобы убедиться, что все так.

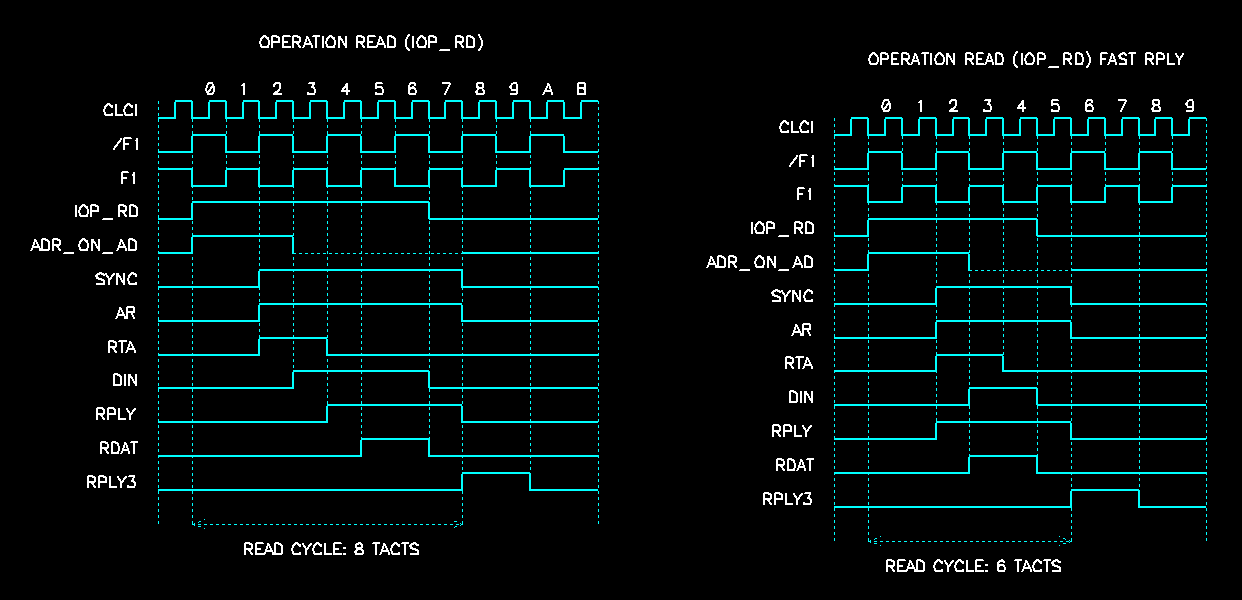

Например, нарисовал, что минимальный цикл чтения занимает 8 тактов. Стал искать лазейки, и выяснил, что если подать упреждающий RPLY синхронный с SYNC, то цикл можно сократить до 6 тактов. Не знаю, хак это или штатно так положено. И вообще, промоделировать такое не могу, может только владелец модели @Vslav. Но как тема для размышления - интересная.

Графики привожу сокращенные, оставив основные сигналы, а то простыня будет на всю страницу.

Код:Описание цикла чтения IOP_RD с нормальной последовательностью сигналов (8 тактов): Начальные условия: BFREE=1 (SYNC=0, AR=0, (RPLY=0 или ARDY=1)) (шина свободна) Начинается F1=0: Такт 0: IOP_RD=1 (цикл чтения), WRA=1 (обновлен регистр адреса RA), BUS_ADR=1 (на шину выставляется адрес). Такт 1: Ничего не происходит (вероятно, чтобы подольше подержать адрес на шине) Такт 2: SYNC=1 (строб записи и анализа адреса ведомыми устройствами), RTA=1 (что это?). Такт 3: Если SYNC заведен на AR, то в этом такте процессор получает подтверждение принятия адреса. AR может быть зафиксирован только в течение нечетного такта (F1=1). Моментально по приходу AR (в любой момент нечетного такта) выставляется DIN=1, Шина переводится в Z-состояние, а сигнал RPLYS=0 (готовность принятия ответа RPLY). Такт 4: Если устройство уже ответило сигналом RPLY, то он будет зафиксирован в этом такте. RPLY может быть зафиксирован в любом четном такте (F1=0), даже в такте 2 или 0, а принят к обратботке начиная с такта 3. Такт 5: В ответ на RPLY в нечетном такте (F1=1) формируется RDAT=1 (чтение данных с шины), который длится 2 такта. Такт 6: Продолжение чтения данных с шины. Такт 7: Снимается сигнал DIN. Внешнее устройство может снимать RPLY. Если устройство не успело снять RPLY до окончания такта 9, то начало DIN следующего цикла будет задержано за счет продлевания REPLY3 на 2 и более тактов (кратно 2 тактам). Такт 8: Снимается сигнал SYNC, может быть начат следующий цикл.

Ответить с цитированием

Ответить с цитированием