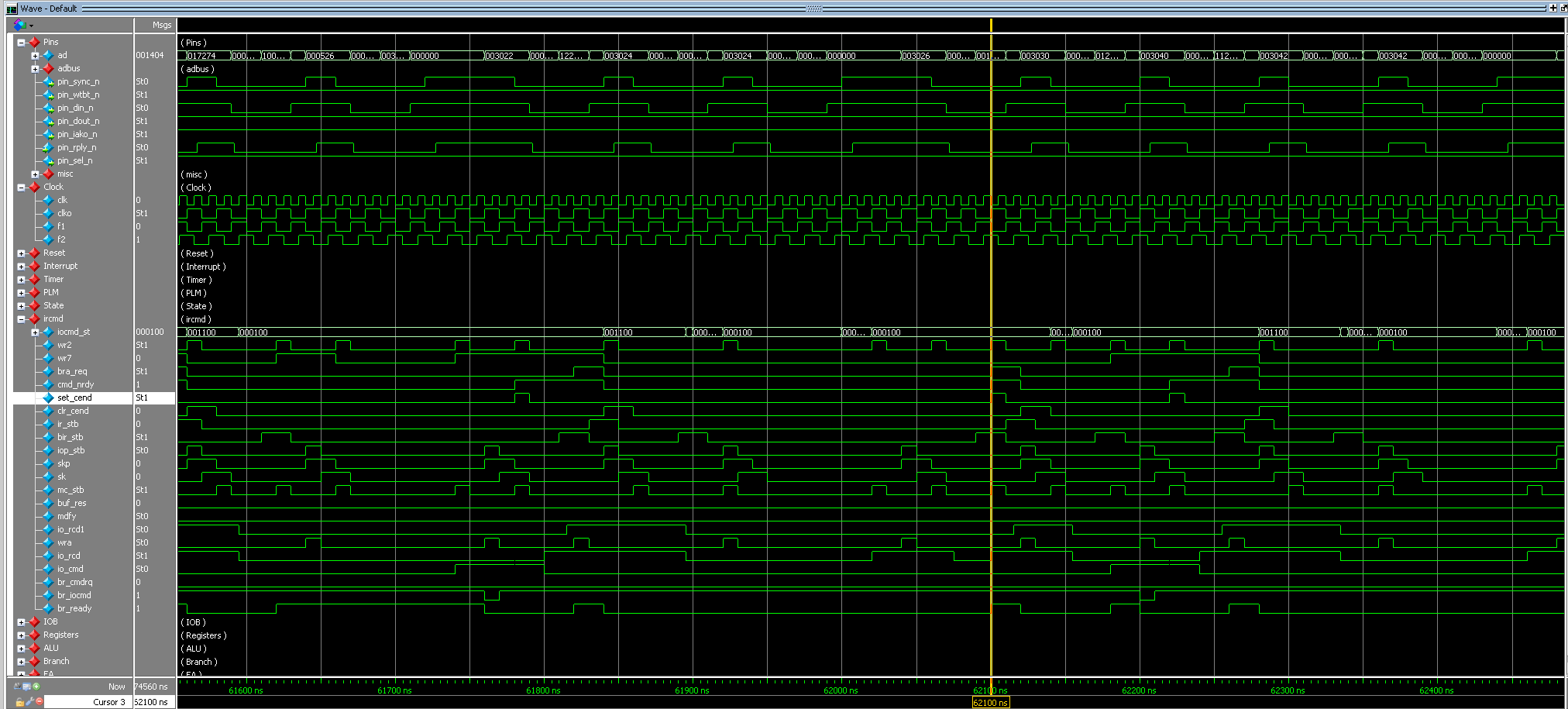

Если уж совсем не повезет, то будет оба низких на выходах, и состояние IR_STB и CLR_CEND просто нее изменится. Две единицы на выходе не бывает, иначе на T17408/17409 мы увидели бы сквозной ток. Но это ты взял совсем сложный кусочек, таких там немного. Это можно обработать только при помощи моделирования, глядя на диаграмму соотношение сигналов становится понятным.

И все сигналы привязаны к изменению фаз, то есть, грубо можно выделить четыре события в периоде - фронты и срезы F1 и F2, и все изменения привязать к ним, временем распространения можно пренебречь, понятно, что в реальном процессоре тактовая частота такая, что все успевает. Главная сложность тут в том, что сигнал может распространяться через латч и нужно отловить все латчи на одной фазе в цепочке и откорректировать распространение для флип-флопов, иначе сигнал запоздает на такт(ы). Такие косяки часто вылавливались по общему фейлу теста или по изменению числа тактов на весь тест. Все тесты T40x на асинхронной модели и синхронной выполняются одинаковое количество тактов. Ну и когда применили модель в реальной системе и попытались запустить 055-ую прошивку повылазила пара проблем, связанных с пультовым режимом, который T40x не проверяет основательно. Поэтому буду делать еще проект ДВК и буду гонять ПЗУ и грузить RT-11 для более полного покрытия. И то это не гарантия, а просто верификация.

Ответить с цитированием

Ответить с цитированием