До чтения аргументов из памяти еще не дошел. Как дойду, расскажу.

А вот до записи в память дошел уже на примере базовых команд типа LD (dd),r.

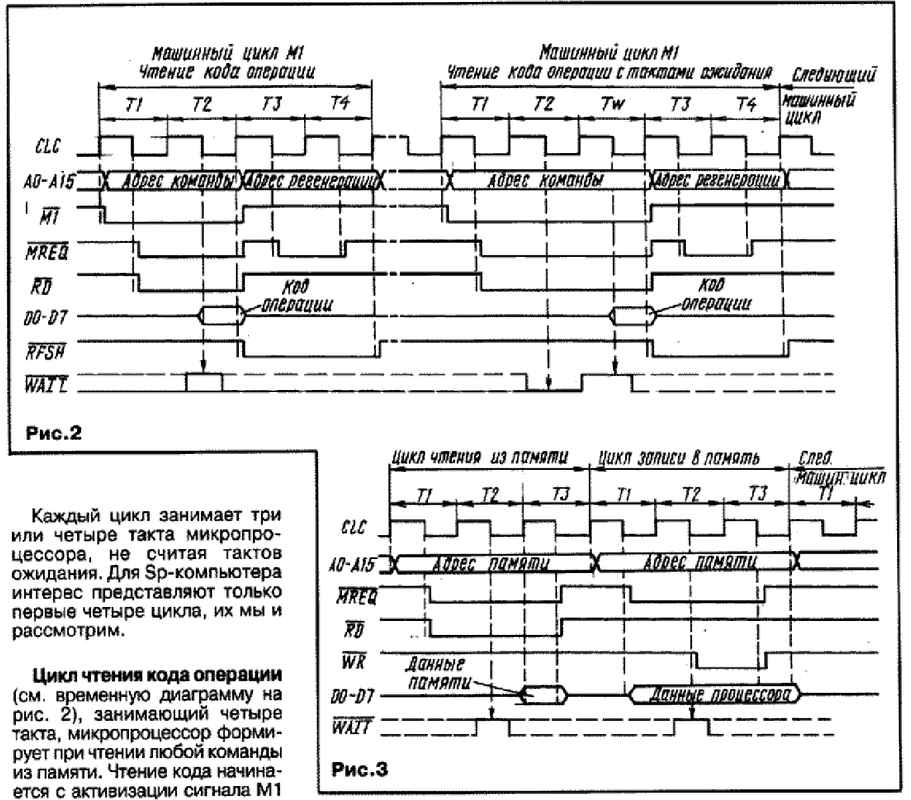

Интересно, что все 3 последних такта команды (цикл M4) посвящены записи байта в память.

Причем, цикл записи длится значительно дольше (2.5 такта после выставления адреса), чем цикл чтения (1.5 такта после выставления адреса).

Не знаю, с чем это связано. Может считалось, что на заре компьютеров запись в память происходила медленнее, чем чтение?

Думаю, если бы на запись отвели не 2.5 такта, а 1.5, как и на чтение, то такие команды, как LD (dd),r занимали бы 6 тактов, а не 7.

Ответить с цитированием

Ответить с цитированием

Размещение рекламы на форуме способствует его дальнейшему развитию

Размещение рекламы на форуме способствует его дальнейшему развитию